Последната

актуализация

на този

раздел е от 2021

година.

§ 6.2

Особености

в

структурата

на основната

памет

Най-често

адресируемата

единица в

основната

памет има

дължина един

байт. Понятието

адресируема

единица

определихме

в раздел 4.1.

Често

адресируемата

единица

наричаме клетка.

Обръщението

към дадена

адресируема

единица (или

още клетка)

се извършва

от процесора,

чрез

подаване на

нейния адрес.

Тъй като обикновено

цикълът за

обръщение

към паметта е

по-дълъг от

този на

процесора,

конструкторите

търсят различни

подходи за

компенсиране,

за ускоряване

на процесите

при обмен,

чрез един или

друг начин за

структуриране

на основната памет.

В същият този

план

разсъждават

и конструкторите

на

интегралните

схеми, в структурата

на които те

също залагат

различни схемни

решения за

“изглаждане”

на процеса на

обмен.

Известно е,

че

бързодействието

на всяко запомнящо

устройство

се снижава с

увеличаване

на неговия

обем. От тук

следва, че за

да се намали

цикълът на

обръщение,

обемът на ЗУ

следва да се

ограничава,

така че да се

спазят

проектните

технически

параметри.

Съществуват

и други

причини, като

например

технологическото

разсейване

на параметрите

на отделните

схеми,

възможност

за реализация

на различни

търговски

конфигурации

и др., които

налагат

подобно

ограничение.

Структурирането

на основната

памет

съответства

на

структурирането

на адреса, т.е.

на адресното

пространство

на процесора,

което пък се

определя по

време на

неговото

проектиране.

Тук нямаме

предвид

структурирането

на паметта по

предназначение,

например отделно

за данни и за

програми.

Няма да имаме

предвид и

структурирането,

с което се

занимава операционната

система, тъй

като то се

отнася до

управлението

и

поддържането

на заетите и

свободните

области като

части на

физически

съществуващите

области.

Често

адресното

пространство

на процесора

не е

реализирано

(изпълнено)

изцяло с

реални

запомнящи клетки.

В адресното

пространство

има свободни

области, а

тези които са

заети или

просто са

физически

съществуващи,

могат да

бъдат реализирани

със различни

запомнящи

устройства.

Типичен

пример е ROM

паметта,

съдържаща BIOS

(базовата

входно-изходна

система) на

една типична

компютърна

конфигурация,

заедно с други

видове RAM динамични

памети.

Ще

разгледаме

по-долу

най-често

прилаганите

подходи за

структуриране

на основната памет.

А) Организация

на паметта по

банки и

модули

За

по-лесно

технологично

реализиране

на основната

памет

адресното

пространство

на даден

процесор

може да се

раздели

формално на

равни по обем

части. Ще

припомним, че

по-рано тук в

глава 4,

обемът М на

адресното

пространство,

беше

определен

чрез дължината

на адреса k (вижте (4.1.1)).

Всяка такава

част от така

разделеното

адресно

пространство

се нарича банка.

Структурирането

на адресното

пространство

по този начин

води до

следното

структуриране

на самия

адрес, дължината

на който сега

може да се

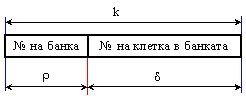

запише така: k=(r+d) [b] :

Фиг. 6.2.1.

Структурно

деление на

адреса при

последователни

банки

Така, дадена клетка от паметта се определя като принадлежаща на банка №i, с пореден номер в банката №j, където посочените произволни номера i, j се определят чрез параметрите на разделения адрес както следва:

![]()

Модулите

на двоичните

полета в

адреса изразяват

съответно

броя на

банките R и

обема на

всяка банка Q:

![]()

Тук

следва да

подчертаем,

че от гледна

точка на

процесора, клетките

в една банка

са с

последователни

адреси.

Описаното

разделяне,

поради

намаляване на

обема на

структурната

единица, т.е.

на отделната

банка,

способства

за нейното

по-лесно

реализиране

(произвеждане)

като отделен

физически модул

– най-често

във вид на

отделна

платка. Всеки

модул сам по

себе си

представлява

запомнящо

устройство с

определен

обем и със

свои собствени

регистри -

адресен и

даннов.

Обемът на

физическия

модул може да

бъде по-малък

или да бъде

равен на

обема на

банката, но

не може да

бъде

по-голям.

Така цялото

адресно

пространство

може да бъде

реализирано

чрез едно

последователно

нареждане на модулите,

което

формира така

наречената физическа

памет.

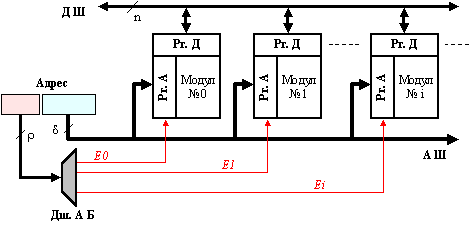

Свързването

на модулите е

чрез общи

адресна и

даннова шини,

както е показано

на фигура 6.2.2.

Фиг. 6.2.2.

Физическа

памет от

последователни

модули

От

фигурата се

вижда, че

адресът,

който излиза

от процесора,

се разделя и

разпространява

физически

по 2 шини,

първата от

които попада

на външен за

модулите

дешифратор Дш.АБ

(дешифратор

на адреса на

банката).

Дешифрирането

на старшата

част от

адреса

формира разрешаващите

сигнали E (Enable) до всеки

отделен

модул.

Младшата

част на адреса

представлява

линейния адрес

в

пространството

на банката,

който е общ

за всички

банки, но е

актуален

само за онзи

модул, който

е получил

активен

разрешаващ

сигнал E. С

помощта на

таблица 6.2.1,

представена

по-долу,

илюстрираме

разделянето

на адресното

пространство.

Въз основа на

представата

ни за него

(вижте фигура

4.1.1) можем да

твърдим, че

последователно

формираните

банки са

разположени

“вертикално”

една под

друга в

адресното

пространство.

Таблица 6.2.1

Разпределение

на адресите в

банките

|

№ на банка r[b] |

№ на клетка в

банката d[b] |

Състав на

адресите в банките |

|

000 … 00 000 … 00 . . . . . . . . . 000 … 00 000 … 00 |

000000 … …

… … 000 000000 … …

… … 001 . . . . . . . . . . . . . . . . . . . . . . 111111 … …

… … 110 111111 … …

… … 111 |

Банка № 0 |

|

000 … 01 000 … 01 . . . . . . . . . 000 … 01 000 … 01 |

000000 … …

… … 000 000000 … …

… … 001 . . . . . . . . . . . . . . . . . . . . . . 111111 … …

… … 110 111111 … …

… … 111 |

Банка № 1 |

|

. . . . . . . . . . . . . . . |

000000 … …

… … 000 000000 … …

… … 001 . . . . . . . . . . . . . . . . . . . . . . 111111 … …

… … 110 111111 … …

… … 111 |

Банка № i |

|

111 … 11 111 … 11 . . . . . . . . . 111 … 11 111 … 11 |

000000 … …

… … 000 000000 … …

… … 001 . . . . . . . . . . . . . . . . . . . . . . 111111 … …

… … 110 111111 … …

… … 111 |

Банка № (R-1) |

В представената структура може да се реализира повишена производителност на обмена, ако се различава функционалното предназначение на отделните банки. Така например, програмният обмен на процесора с дадена банка може да бъде съвместен с прекия достъп до друга банка, осъществяван чрез контролера за пряк достъп до паметта.

В такава структура лесно може да се изключи от общата система банка, чийто модул е повреден, с последващо прегрупиране на годните за експлоатация банки. В тази връзка отново ще припомним, че непрекъснато физическо пространство може да бъде реализирано само ако модулите имат обема на банките. Ако обема на модулите е по-малък в адресното пространство ще се образуват области с физически нереализирани клетки, който факт може да доведе до грешни обръщения, ако липсва система за защита на паметта. Нарастването на обема на физическата памет чрез добавяне на нови модули е възможно при условие, че обемът им е равен или по-малък от този на банката, което в практически условия е едно доста строго ограничение и това е определено неудобство при експлоатацията на такива системи. В защита на тази структура обаче следва да кажем, че в системи, където данновата шина на процесора е с ширина равна разрядната мрежа тя е възможно най-простата.

Б) Организация

на паметта по

разслоени

банки

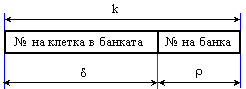

Структурирането на адресното пространство чрез структуриране на адреса на две части може да бъде извършено по още един начин, който води до друга интерпретация на адресното пространство. Както и в предидущия случай, структурата на адреса се дели на две част, показани на фигура 6.2.3.

Фиг. 6.2.3.

Структурно

деление на

адреса при

хоризонтални

банки

От

фигура 6.2.3 се

вижда, че

разглеждаме

този случай

при

условията на

предидущия –

общият обем

на адресното

пространство

е същия и

разделянето

е на същия

брой банки.

Разликата е в

това, че сега

техните номера,

т.е. адреси, са

разположени

в младшата част

на адресното

поле. Това

структуриране

води до

ситуацията, в

която когато

от процесора

се подават

последователни

адреси, същите

ще бъдат

откривани в

различни

банки. С

помощта на

таблица 6.2.2,

представена

по-долу,

илюстрираме

разделянето

на адресното

пространство.

Таблица 6.2.2

Разпределение

на адресите в

банките

|

№ на клетка в

банката d[b] |

№ на банка r[b] |

Редуване на

банките |

|

000000 …

… … … 000 000000 …

… … … 000 000000 …

… … … 000 000000 …

… … … 000 . . . . . . . . . . . . . . . . . . . . . . 000000 … …

… … 000 000000 …

… … … 000 |

000 … 00 000 … 01 000 … 10 000 … 11 . . . . . . 111 … 10 111 … 11 |

Банка

№ 0 Банка

№ 1 Банка

№ 2 Банка

№ 3 . . . . . .

Банка № (R-2)

Банка № (R-1) |

|

000000 …

… … … 001 000000 …

… … … 001 000000 …

… … … 001 000000 …

… … … 001 . . . . . . . . . . . . . . . . . . . . . . 000000 … …

… … 001 000000 …

… … … 001 |

000 … 00 000 … 01 000 … 10 000 … 11 . . . . . . 111 … 10 111 … 11 |

Банка

№ 0 Банка

№ 1 Банка

№ 2 Банка

№ 3 . . . . . .

Банка № (R-2)

Банка № (R-1) |

|

. . . . . . . . . . . . . . . . . . . . . . |

. . . . . . |

. . . . . . |

|

111111 …

… … … 111 111111 …

… … … 111 111111 …

… … … 111 111111 …

… … … 111 . . . . . . . . . . . . . . . . . . . . . . 111111 … …

… … 111 111111 …

… … … 111 |

000 … 00 000 … 01 000 … 10 000 … 11 . . . . . . 111 … 10 111 … 11 |

Банка

№ 0 Банка

№ 1 Банка

№ 2 Банка

№ 3 . . . . . .

Банка № (R-2)

Банка № (R-1) |

Въз

основа на

горната

таблица и

предварителната

ни

представата

за адресното

пространство

(вижте фигура

4.1.1) можем

да твърдим,

че при това

структуриране

на адреса,

клетките в

адресното

пространство

не са

подредени в една

колонка и не

съответстват

на

досегашната

ни векторна

представа за

паметта.

Според

представеното

структуриране

последователните

адреси на

клетките се

подреждат по

редове и колонки

или с други

думи в един

ред са подредени

банките, а в

тях, като в

колонка, са

включени

клетки от

последователни

подмножества

(сечения) от

непоследователни

адреси със

стъпка равна

на броя на

банките. Това

подреждане е

удобно да се

интерпретира

като матрично,

а

структурирането

е известно

под името разслоено

адресиране.

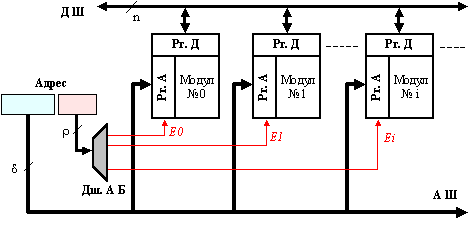

Физическа памет с модули, реализиращи разслоено адресиране, е показана на фигура 6.2.4.

Фиг. 6.2.4.

Физическа

памет от

“редуващи се”

модули

Същността

на

показаното

структуриране

се изразява в

това, че

всяка

физическа

банка има

точно определено

място, при

което

адресираната

с адрес А

клетка се

намира в

банка, чийто

номер е равен

на A(modR).

Например, ако

адресът е А=R+2 , това

означава, че

той се намира

в банка, чийто

номер е 2, тъй

като [R+2](modR)=2.

Реализирането

на

физическата памет

по

представения

начин

изисква задължително

поставяне на

всички R модули.

Не е възможно

да липсва

модул, още повече

в произволно

място, тъй

като липсата му

означава, че

се нарушава

последователното

следване на

физическите

клетки. Липсата

на модул, реализиращ

дадена банка

е невъзможно

да се “поправи”

със средства

от

операционната

система,

както това

беше

възможно в

предидущата

структура.

Освен това,

структурата

с разслоено

адресиране

изисква

всички

модули, изграждащи

хоризонталните

редове, да

имат един и

същи обем.

Модулите в

един

хоризонтален

ред на

физическата

памет могат

да имат обем по-малък

от обема на

банката Q. В този

случай

допълването

на обема до

максимално

възможния Q е

възможно с

добавяне на

втори, трети

и т.н. редове

от модули,

чийто обем

обаче следва

да бъде

кратен на 2,

така че да е

възможно

тяхното

разрешаване

(дешифриране)

във

вертикално

направление

чрез

старшите битове

на адреса.

Ако е необходимо да се извлече информация от няколко последователни адреса по n-битовата даннова шина (например дълъг операнд разположен на порции хоризонтално, в клетки от първата до последната банка), трябва да се инициира обръщение към всяка банка поотделно и последователно. При тази структура съществува възможност за конвейерна организация на трансфера, т.е. след иницииране на обръщението към поредната банка, да се пристъпи към иницииране на обръщение към следващата банка, без да се чака завършване на операцията в текущата. Този начин на организация на процедурата за четене или за запис на информация, позволява паралелна работа на физически самостоятелните банки, в резултат на което продължителността на процедурата се намалява или с други думи производителността се повишава. Описаното разслоено адресиране и конвейерна организация на достъпа са реализирани в логическата структура на RAM паметите с голям обем, като показаната на фигура 4.2.2.3.

Възможна е още и така нареченото пакетно обръщение. Реализацията му се основава на факта, че адресната шина е обща за всички банки. Това означава, че едноименните клетки (клетките от един ред) във всяка банка ще бъдат едновременно отворени и свързани с данновите регистри Рг.Д. Съвместната работа на данновите регистри с общата даннова шина (при четене на съдържанието им или при запис на данни в тях) се организира във времето чрез мултиплексирането им върху последната с помощта на разрешаващите сигнали от дешифратора на адреса на банките Дш.АБ, както е показано на фигура 6.2.4. Така при последователни адреси значително по-бързо могат да се обменят порции данни с дължината на един ред от физическата памет.

Подходът на разслоените адреси има един съществен недостатък, който се състои в това, че при повреда на една от банките, цялата памет се оказва неработоспособна. Може да се каже още, че производителността на основната памет, при четирикратно разслоение, се повишава от 1,5 до 2 пъти.

В) Паметта

като общ

ресурс

Производителността на компютърната система може да бъде повишена чрез прилагане на асинхронния метод за управление на ниво устройства. Това означава, че на паметта се дава възможност, като самостоятелно и общо устройство, да обслужва освен процесора и останалите устройства, като ги третира като свои клиенти, или като свои абонати. В момента на обслужване на даден абонат останалите са свободни да изпълняват други функции, с което се дава възможност за относителен паралелизъм между процесите протичащи в паметта и всички останали устройства. В резултат на това се твърди, че се повишава производителността на системата като цяло.

За

организация

на достъпа на

абонатите (процесор,

канал за пряк

достъп,

контролери

на външни

устройства)

до паметта,

се въвежда

определена

дисциплина

на

обслужване - "според

реда на

пристигане

на заявките",

или с други

думи се

организира

опашка от тип

FIFO. По силата на

това правило,

достъп получава

устройството,

което първо е

подало

заявка за

обмен. Тъй

като

съществува

вероятност в

един и същи

момент да

пристигнат

едновременно

няколко

заявки, което

представлява

явен

проблем за

паметта, във

връзка с

необходимостта

да се направи

избор, на

последните

се приписва приоритет.

Ако приемем,

че броят на

банките е 4, то

изборът на

заявка за

обмен се

осъществява

с помощта на

логическата

схема,

показана на

фигура 6.2.5.

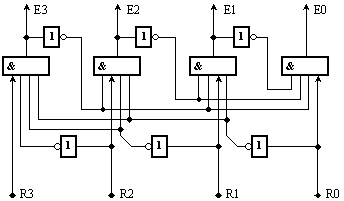

Фиг. 6.2.5. Схема

за избор

На схемата

са показани

четири входа за

заявки R0, R1, R2 и R3, и

четири

разрешаващи

изхода - E0, E1, E2 и E3. Логиката на

изходите се

изразява

чрез следната

логическа

функция:

![]()

В схемата от

фигура 6.2.5 тези

функции имат

следния вид:

![]() (6.2.4)

(6.2.4)

Според

логиката на

схемата, ако

са подадени

всички

заявки

едновременно,

само на първи

изход ще има

разрешаващ

сигнал, т.е. E0=1, E1=E2=E3=0.

От тук следва,

че

най-приоритетен

е вход №0, и постъпващата

там заявка R0 се

обслужва

винаги първа.

От

множеството

абонати

обикновено

най-високо

бързодействие

има

процесорът,

ето защо той

представлява

абонат с

най-нисък

приоритет.

Постъпва се

така, защото

в процесора няма

опасност от

загуба на

информация,

докато във

външните

устройства,

работещи с механично

движещи се

носители,

такава

възможност съществува.

В случаите,

когато

оперативната

памет

извършва

обмен с

външно

устройство,

заявката на

процесора не

се приема и

той следва да

изчака. Този

режим на

работа на процесора

се нарича

режим на

задържане.

Производителността

на процесора

зависи от интензивността

на обмена

между

оперативната

памет и

външните

устройства.

Г) Увеличена

разрядност

на данновата

шина

Във

връзка с

повишаването

на

производителността

на основната

памет

особено

актуален е

подходът,

свързан с

увеличаване

на ширината

на данновата

шина на

процесора.

Особено

интересен е

случаят, при

който

данновата

шина е

по-широка от

дължината на

разрядната

мрежа, от

което веднага

следва

изводът, че

за един цикъл

ще могат да

се

трансферират

(обменят)

повече от

един

операнди.

Увеличаването

на разрядността

на данновата

шина е

възможно

най-тривиалният

подход към

повишаване

на производителността

на основната

памет. Така

например, при

еднобайтова

шина един

четирибайтов

операнд ще се

обменя за

четири

цикъла. При

положение, че

данновата

шина се

разшири до 32

бита, същият

операнд ще се

обменя

четири пъти по-бързо.

В

съвременни

условия,

когато

форматите на данните

в разрядната

мрежа

варират от 1

до 8 и повече

байта,

ширината на

данновата

шина е

параметър от

изключително

значение за

производителността

на обмена с

основната

памет. Като

имаме

предвид, че

типичната

дължина на

адресируемата

единица (на

запомнящата

клетка)

продължава

да бъде 8[b], ширината

на данновата

шина

предопределя

вида на

структурирането

на основната

памет.

Следващият

раздел е:

6.3.

Особености

в

структурата

на буферната

памет