Последната

актуализация

на този

раздел е от 2021 година.

Г Л А В А 6

ОРГАНИЗАЦИЯ НА ЗАПОМНЯЩАТА СИСТЕМА

§ 6.1

Йерархична

структура на

компютърната

запомняща

система

Всеки

потребител

лесно се

убеждава, че

компютърната

памет е

желателно да

бъде колкото

се може

по-голяма по

обем и да

работи

възможно

по-бързо. За

съжаление

тези два

критерия, по

които

обикновено

оценяваме

паметта трудно

могат да

бъдат

удовлетворени

чрез използването

на един

единствен

тип запомнящи

устройства.

Нещо повече,

изборът на

запомнящи

устройства

се влияе още

от такива

техни

характеристики

като: цена,

консумация

на енергия,

габаритни

размери и др.

Ето защо

компютърната

запомняща

система се изгражда

като йерархическа

система, в

която по

възможно

най-оптимален

начин се съчетават

различни по

тип

запомнящи

устройства,

като такива с

високо

бързодействие,

имащи висока

цена и в

същото време

не особено

голям обем и

запомнящи

устройства

със средно и

ниско

бързодействие,

но с голям

обем и ниска цена.

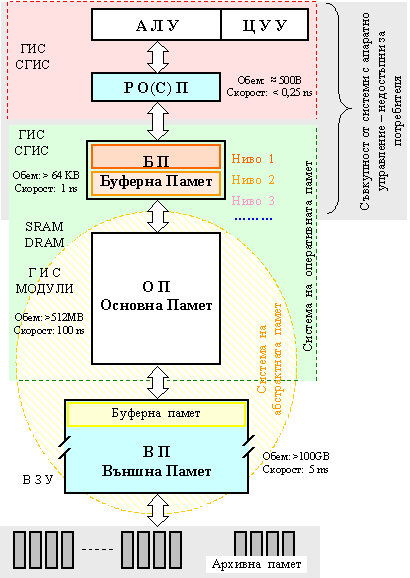

По-долу на

фигура 6.1.1 е

показана общата

йерархична

представа за

компютърната

запомняща

система.

Фиг. 6.1.1. Йерархична

структура на

компютърната

запомняща

система

Най-близо

до

операционната (изчислителната)

част на

процесора,

т.е. до АЛУ, се

намира регистровата

памет (РП).

Тук нямаме

предвид

регистрите,

които са съставна

част от

логическата

структура на АЛУ,

а само онези,

които са

програмно

достъпни.

Противно на

нашето

мнение

читателят може

да намери

множество

публикации, в

които всички

работни и

системни регистри

от

логическата

структура на

операционната

част на

процесора, са

включени в разбирането

за

регистровата

памет.

Съвкупността

от регистри е

предназначена

да обслужва

вътрешните

потребности

на процесора

за

съхраняване

на данни.

Функционалното

предназначение

на отделните

регистри

може да бъде

фиксирано

или

нефиксирано

(свободно).

Регистровата

памет

обикновено

се нарича регистров

файл или още

просто регистри

с общо (и/или

специално)

предназначение

(РО(С)П).

Наборите от

регистри в

един процесор

могат да бъдат

няколко и с

различни

наименования,

които

обслужват

различни

негови

функции и потребности.

Последното

означава, че

те могат да

се съдържат в

логическата

структура на

различни,

както

операционни,

така и управляващи

устройства.

Регистрите

могат да бъдат

достъпни или

недостъпни

за

потребителя.

Някои от

регистровите

набори биват

наричани

таблици или

буфери.

По-надолу

в йерархията

на паметта

стои буферната

памет (БП), а

после

следват основната

(или още

първичната)

памет (ОП);

вторичната (или

още външната)

памет (ВП) и архивната

памет (АП). От

всички тези

памети, обект

на внимание

тук в тази

глава, ще

бъде

организацията

само на

буферната и на

основната

памети.

Буферната

памет,

както може да

се разбира от

нейното

наименование,

има за задача

да буферира

информационния

поток между

две нива в

йерархическата

система, като

при това

съгласува

различните

скорости за

достъп в

отделните

нива на

паметта.

Буферната

памет е

междинно, спомагателно

и

съгласуващо

звено и като

такова

следва да

остава

скрито за

основните нива.

Нещо повече,

това звено

следва да

бъде проектирано

така, че

неговото

функциониране

да не зависи

от

потребителя.

Както е

показано на

фигура 6.1.1

по-горе, в

съвременните

процесори

буферната

памет от само

себе си

представлява

силно

развита и

сложно

организирана

йерархична

подсистема,

съдържаща 3 и

повече нива.

От към нивото

на основната

памет, във

връзка с

възможностите

на

съвременните

интегрални

технологии,

се

различават "вътрешна"

и "външна" буферни

памети, в

зависимост

от разположението

ѝ върху

кристала на

интегралната

схема на

процесора. В

литературата

като цяло

буферната

памет

обикновено

се нарича кеш-памет,

т.е. скрита

памет.

Дори

за

съвременните

технологии

първичната

памет е бавна

в сравнение

със скоростите

в процесора

(имаме

предвид

скоростите за

обмен на

данни).

Високоскоростната

преработката

на данни в

процесора

може реално

да бъде забавена

от бавния

процес за

доставка на нови

данни от

паметта. В

този смисъл

дисбалансът

между тези

две нива в

запомнящата

система е

обект на

специално

внимание.

Именно за да

се намали

ефектът от

това

несъответствие

в скоростите

на обмен на

данни между

процесора и

основната

памет се

въвежда буферната

памет. Идеята

е проста и се

основава на

разбирането,

че буферната

памет може да

играе роля на

посредник

между двете

нива, който

при

необходимост

поема в

подходящо време

управлението

върху

трансфера на

данните. Или

още в друга

интерпретация

-

буферната

памет може да

се възприема

като резервоар,

който се

пълни (или

изпразва) с ниска

скорост с

данни от (в) ОП,

които в

същото време

могат да се

предоставят

(или приемат)

при необходимост

с голяма

скорост от

процесора.

Ето защо

елементната

база за

реализация на

буферната

памет трябва

да бъде с

високо бързодействие.

Това

изискване се

постига чрез

реализация

на тази памет

върху кристала

на самия

процесор, или

от външна,

специално реализирана

и

непосредствено

поставена бърза

памет,

например, от

тип SDRAM (от 10 до 100 пъти

по-бърза от

основната

памет).

При

комплексна

реализация

на

изказаните структурни,

организационни

и апаратни условия

се очаква

като цяло

повишено

бързодействие

на

изчислителния

процес.

Най-съществена

заслуга за

това има

идеята, както

вече казахме,

за

предварително

"напомпване"

на

най-вероятната

за

непосредствено

използване

информация в

буфера така,

че при необходимост

тя да бъде

доставена

незабавно на

процесора.

В

реалните

системи

високата

скорост се осигурява

от една

страна чрез

бързодействащи

схеми, от

друга страна

чрез

разполагането

им на много

малко

разстояние

от процесора

(включително

чрез

разполагане

върху кристалната

подложка на

самия

процесор) и

на трето място

чрез

специални

структурни

решения. Важно

е още тук да

подчертаем,

че целият

този механизъм

(имаме

предвид

структурните

решения)

трябва да

бъде скрит

от

потребителя

(или още от

процесора),

който

разглежда

паметта като

напълно

хомогенно

устройство.

Това е така

защото при

изпълнение

на основна операция

(четене или

запис)

машинната

команда не

разполага с

нищо друго

освен с

адреса на

операнда или на

следващата

команда.

Операциите

по обмен с

буферната

памет са напълно

автоматизирани,

т.е. тяхното

управление е

апаратно.

Така от

гледната

точка на

програмиста,

буферната

памет не се

различава като

отделен

структурен

елемент на

паметта. За

съжаление

този статут

на буферната

памет се

постига

изключително

трудно, ето

защо в някои

реални

процесори

има известни,

макар и силно

ограничени

възможности

за нейната

манипулация.

Механизмът,

по който се

обслужват

операциите

на обмен

между

процесора и

първичната памет

при

наличието на

буферна

памет, се основава

на достъп от

вида FIFO, или на

асоциативен

достъп.

Същите са

допълнително

усложнени в

сравнение с

класическите

методи за

достъп,

разгледани

тук в глава 4

на тази

книга.

Основната

памет,

главното

изискване

към която е

да бъде възможно

с по-голям

обем, се

изгражда от

по-евтини запомнящи

интегрални

схеми,

най-често

динамични,

т.е. DRAM. В тази памет,

наричана още оперативна,

се съдържат

данните и

командите на

всяка активна

потребителска

програма.

Основната

памет изпълва

физически

адресното

пространство

на процесора

(или отделни

негови

области).

Обменът с

основната

памет от страна

на процесора

най-често е

съгласуван по

бързодействие,

дори

синхронен,

особено в

случаите на

по-тривиални

компютърни

конфигурации,

когато

буферната

памет въобще липсва

като такава

(вижте

времедиаграмите

от фигурите в

глава 4,

пункт 4.2.1

и пункт

4.2.2). Под

съгласуван

имаме

предвид

параметрите

на тактовите

последователности

за процесора

и за чиповете

на паметта.

Следващото

ниво в

йерархията

на запомнящата

система е външната

памет.

Външната

памет се

характеризира

със своята

специална

реализация.

От една

страна

нейната

паметливост

се реализира

непосредствено

в така

наречените носители

на

информация.

Тук най-често

подразбираме

магнитни или

оптични

носители, от

които снемането

както и

поставянето

на информация

е свързано с

механично

движение.

Процесите на

запис и

четене от

такива

носители се

реализира

върху

специално

проектирани

устройства,

които ние

най-общо ще

наричаме външни

запомнящи

устройства

(ВЗУ). От друга

страна

паметта,

реализирана чрез

външните

запомнящи

устройства

има много

голям обем

(обикновено

надхвърля

100-кратно

обема на

основната памет).

От трета

страна

скоростта на

изпълнение

на операции

от тип четене

и запис в тази

памет е много

по-ниска от

тази в

основната

памет, така

че проблемът

дисбаланс в скоростите

на обмен

между тези

две нива е реален

и той се

решава с

помощта на

същия подход,

който беше

разгледан

по-горе –

вмъкване между

двете нива на

буферна

памет.

Реализацията

на външната

памет в

съвременни

условия е

силно

повлияна от

развитието

на интегралните

технологии.

Вече писахме

за това в 4-та

глава на

тази книга,

като

изтъкнахме

възможностите

на флаш

паметите,

благодарение

на които

много

типични

външни

устройства

имат свои

съвременни електронни

реализации.

Запомняща

система, в

организацията

на която се

използува

специална

концепция и механизъм,

с помощта на

които

значително

се разширява

обемът на

основната

памет, чрез разширяване

на адресното

пространство

на процесора

върху външни

запомнящи

устройства,

се нарича виртуална

(или още

хипотетична)

памет.

Адресното

пространство

на

виртуалната

памет се

дефинира

чрез

значително

удължаване

на адресното

поле. Дългият

адрес определя

такъв обем на

паметта,

който

практически

може да се

приеме за неограничен.

Използувайки

това адресно

поле в

качеството

на абстрактен

адрес,

програмистът

може да

разглежда

запомнящата

система като

абстрактна и

хомогенна памет

(има се

предвид от

техническа

гледна точка)

с

неограничен

обем.

Практически

се приема, че

той

разполага с

неограничен

брой клетки

за

съхраняване

на информация.

Йерархичната

запомняща

система се

характеризира

с различни и

сложни

алгоритми за обмен

на

информация

между

различни по

вид запомнящи

устройства,

реализиращи

различните

нива на

системата. За

да се

организира

функционирането

на такава

система се прилага

принципът

за локално

обръщение

към ЗУ.

Принципът на

локалното

действие

често “обличат"

в числена

форма и

наричат това

правило “90/10" –

означаващо 90%

от времето на

работещата

програма е

свързано с

достъп до 10% от

нейното

адресно

пространство.

Същността на

този принцип

се състои в

това, че

разстоянието

между

областите в

паметта,

между които

се извършва

активен

обмен, трябва

да бъде сравнително

малко. В

същото време,

ограничените

по този начин

области,

които имат

по-активен

обмен, следва

да се намират

в по-бързи

запомнящи

устройства.

Така например,

ако

потребителската

програма

активно работи

с данни,

намиращи се в

съседни

клетки, т.е.

ако в тези

клетки

програмата в

текущия период

от време

извършва

многократно

обръщение, то

според

горния

принцип,

адресната област

на тези данни

следва да се

придвижи към

по-високото

ниво в

йерархията

на паметта. Това

придвижване

обаче става

автоматично

и без

знанието на

програмиста.

За да може да

се осигури

това

движение на

адресните области

между

отделните

нива на

паметта, се въвежда

специално

управление

на паметта (апаратно

или

програмно), в

което се

залагат всички

необходими

за целта

алгоритми.

Устройството

за

управление

на паметта

работи съвместно

със

системното

програмно

осигуряване

и по този

начин в

значителна

степен

освобождава

програмиста

от грижите по

разпределение

и поддръжка

на паметта.

При

тези процеси

паметта се

структурира

с помощта на единица

за обмен,

която се

нарича блок или

пакет.

Между

отделните

нива в

системата на

паметта

информацията

се движи

опакована в

тези единици

за обмен, т.е.

по блокове

(пакети). Прехвърлянето

на един блок

от едно ниво

в друго ниво

може да бъде

извършено

ефективно, ако

обемът

на блока е

избран

правилно.

Обемът

(дължината)

на блока е в

пряка връзка

най-вече със

скоростите

на обмен

между отделните

нива (между

отделните

видове ЗУ), а

така също със

състава на

интерфейса

между нивата.

Блоковете

могат да

бъдат

определени

както с

фиксиран,

така и с

променлив

обем. Все пак

съществуват

голям брой

различни компютърни

конфигурации,

които

обменят данни

на ниво

адресируема

единица, т.е.

клетка. Такива

са

обикновено

системите с

по-елементарна

процесорна

архитектура.

Управлението

на паметта

изисква:

а)

Система за

управление

на адресното

пространство

;

б)

Система за

съгласуване

на обмена на

блокове между

отделните

нива ;

в)

Система за

избор на

блокове за

подмяна,

намиращи се в

по-високото

ниво, загубили

активност.

Първата система е длъжна

да води на

отчет

незаетите с

полезна

информация

области в

паметта и да

реагира по

подходящ

начин при

заявки за достъп

в тези

области.

Обикновено,

когато блоковете

от полезна

информация

са с фиксирана

дължина,

управляването

на тяхното

движение не

създава

трудности

при намиране

на свободна

област и при

преподреждане,

с цел обединяване

на

свободните

области.

Такива трудности

възникват

когато

блоковете са

с променлива

дължина.

Втората система управлява

предаването

на блоковете

към

по-високото ниво

в паметта.

Системата е

длъжна да

прехвърли

блок с

полезна

информация

от по-ниско към

по-високо

ниво по

силата на

някакво условие.

Условията,

които се

използуват,

са формулирани

така:

а) Само в

онзи момент,

когато

съдържащата

се в блока

информация

стане

необходима ;

б) Само

когато

настъпи

време за използуване

на

информацията,

определено

отнапред, с

оглед на

предварителна

подготовка

преди

необходимия

момент.

Третата система

организира

последователността

от нуждаещите

се за

прехвърляне

блокове от

високите към

ниските нива

на паметта.

Такава необходимост

се появява в

случаите,

когато втората

система не

може да

осъществи

прехвърляне

поради липса

на свободни

области за

блок, движещ

се от

по-ниско към

по-високо

ниво.

Алгоритмите

за

управление

на паметта

зависят от

общата

концепция на

конструкторите

за

организация

на адресното

пространство

на даден

процесор.

Много за

управлението

на паметта

читателят

може да научи

още от книгата:

Andrew S.

Tanenbaum, Herbert Bos, Modern operating systems, 4-th ed.,

Pearson Education, 2015, ISBN-10:

0-13-359162-X

Следващият

раздел е: