Последната актуализация на този раздел е от 2020 година.

5.5.3 Съвременна

архитектура на входно-изходната система

Архитектурата на входно-изходната система определя възможностите, приложението и цената на една компютърна система. Към това естествено следва да добавим и софтуерното осигуряване. В процеса на “обрастване” на това кълбо от “твърди” и “меки” елементи вземат участие огромен брой компании. Поради изключителната ширина на темата и навлизане в допълнителни теми не можем да си позволим подробно систематическо изложение. Ще се ограничим само върху някои качества на масовите РС-системи. Цялото многообразие от класове в архитектурата на компютърните системи остава извън нашето внимание тук.

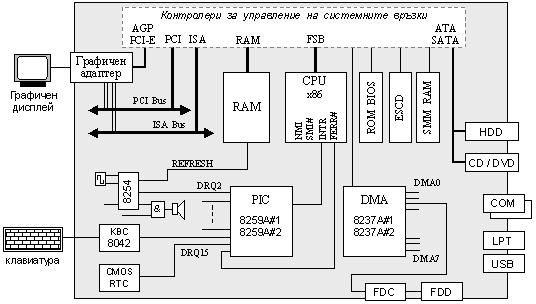

Ще се спрем първо върху състава на една типична IA-32 РС-съвместима платформа, която е илюстрирана на следващата фигура:

Фиг. 5.5.3.1. Състав на компютърна платформа с общо предназначение

Както се вижда от фигурата, в центъра на системата е процесорът (един или няколко) и оперативната памет, представляващи по същество цифровата изчислителна машина. Основен “двигател” на машината е тактовия генератор, в лицето на интегрална схема от типа на номенклатурата 8254 на Intel. Част от паметта, под формата на постоянна памет, съдържа постоянното програмно осигуряване и BIOS, което е предназначено да осигури жизнените функции на работещия компютър. Основните съставни елементи на системата е възможно да бъдат свързани с останалите компоненти чрез няколко различни интерфейса и йерархична система от шини, като например ISA, PCI (PCI-X, PCI-E), AGP и др. Типичната платформа с общо предназначение съдържа набор от общо приети като необходими средства за вход-изход, както и средства за тяхното поддържане. Тук влизат системата за апаратни прекъсвания на базата на PIC-контролери от типа на 8259А, система за пряк достъп до паметта на базата на DMA-контролери от типа на 8237А, интерфейс на клавиатурата (на базата на микроконтролер 8042), схеми за управление на системната звукова сигнализация и часовника за реално време CMOS RTC. Следва да споменем още графичния дисплей и графичния контролер, който по същество представлява сложен процесор, изпълняващ специфични задачи, свързани с визуалното представяне на информацията. Контролерите на шините към периферните устройства ATA, SATA, SCSI, SAS, USB, FireWire, а така също комуникационните интерфейси COM, LPT, GAME и др. И към всичко това следва да добавим още самите външни устройства, като дискове (HDD, FDD, CD, DVD), аудио средства (контролери, усилватели, тунери), принтери, скенери, видеокамери и др. Изредените компоненти от само себе си представляват изключително сложни системи, ето защо с увереност може да твърдим, че компютърната система е едно от най-сложните технически средства, което е навлязло масово в ежедневието ни.

Голяма част от логическите връзки между изброените елементи не са представени на горната фигура. Тази сложна система от логически връзки се реализира и управлява с помощта на голям брой специализирани в своите функции логически устройства, част от които ние вече представихме. Номенклатурата на тези специализирани устройства и схеми съставя така наречената микропроцесорна фамилия интегрални схеми. По същество това е един набор от градивни елементи (отделни интегрални схеми), който има свойството да бъде функционално пълен и да позволява проектирането и изграждането на компютърни системи с различна архитектура.

Благодарение на динамичното развитие на производствените технологии, еволюцията на микропроцесорните фамилии интегрални схеми е изключително интересна. Тя се характеризира с непрекъснато нарастващата интеграция на принципните схеми и като следствие, значително намаляване на градивния брой интегрални схеми, реализиращи съвременните компютърни системи. Интегрирането в един единствен чип на множество специализирани контролери е неотменна съвременна тенденция. Комплектът от такива интегрални схеми е получил общото и нарицателно наименование чипсет (набор от чипове). Със своя вътрешен състав и структура интегралните схеми в чипсетите (в наборите) определят възможностите за използване на определен тип процесори, възможностите за използване на определен тип памети (както оперативна, така и буферна – кеш памет), а така също редица други характеристики на системата, определящи възможностите за нейното модернизиране в бъдеще време при появата на нови и по-производителни компоненти. Удачно подбраният чипсет (набор от интегрални схеми) може да допринесе за повишаване на производителността на една система в сравнение с друга, повече от 20%, при условие, че те са реализирани с един и същи набор от процесор и памет. И това е разбираемо, като имаме предвид, че тези схеми управляват комуникациите по всички входно-изходни шини в системата.

Различните производители на

интегрални схеми за конфигуриране на компютърни системи, включително и тези на

микропроцесори, дадоха възможност за проектиране и реализация на различни по

структура, по възможности и по цена основни, или още наричани “дънни” платки.

Към тях можем да причислим и производителите на периферни устройства и

контролери за тях. В този смисъл стана уместно да се говори за архитектура

на дънната платка, което по същество е архитектура на входно-изходната

система. Отново ще припомним, че темата на този пункт обобщава само масово

произвежданите РС-системи. Ето някои полезни сведения за дънните платки, които

имат следните синонимни наименования: system board, main board, motherboard.

Тези платки се произвеждат по стандартизирани размери и форма. Интегралният

критерий за означаване се нарича формфактор.

Според формфактора (освен чисто фирмените) имаме следните общо приети видове

системни платки:

Таблица 5.5.3.1 Видове формфактори и тяхното приложение

|

ATX |

Стандартни настолни компютри, затворени в кутии mini-tower или full-tower. |

|

Mini-ATX |

Умалена версия на системи АТХ, прилагани вместо системи АТХ. |

|

Micro-ATX |

Среден клас настолни или вертикални системи mini-tower. Имат намалена ширина, намален брой съединители и умален размер на захранващото устройство. |

|

Flex-ATX |

Евтини и по-ниско производителни настолни или вертикални системи mini-tower. |

|

NLX |

Корпоративни настолни или вертикални системи mini-tower, отличаващи се с простота и удобство при обслужване. |

|

WTX |

Workstation Technology Extended – голяма

по размер платка за работни станции с голяма мощност. |

Изброените по-горе формфактори не са единствените. Има предложени, които още не са намерили широко разпространение или се очаква това да стане в бъдеще. Такива са ВТХ (Balanced Technology Extended) и Pico BTX на Intel; Mini ITX (на VIA) и Nano ITX с размери 12х12 сантиметра; SFF (Small Form Factor) и др.

На системната платка се намират:

1. Цокъл (гнездо, слот, съединител) за микропроцесора;

2. Набор интегрални схеми за системната логика (северен и южен мостове или хъб);

3. Интегрална схема Super I/O;

4. Базова система за вход-изход (ROM BIOS);

5. Слотове за модули оперативна памет (SIMM/DIMM/RIMM);

6. Слотове за PCI, AGP-карти;

7. Гнездо ARM (Audio Modem Riser);

8. Гнездо CNR (Communications and Network Riser);

9. Преобразовател на захранващо напрежение за процесора;

10. Батерия.

Процесорите могат да се поставят в цокъл тип Socket или Slot. По номера на модела на гнездото може да се определи какъв модел процесор може да се поставя.

Историческа

обусловеност

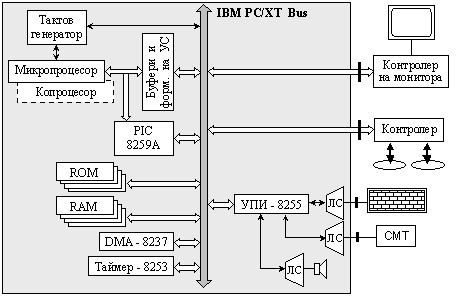

В ранните компютърни системи, построени върху микропроцесорите i86 (i87), задачата на допълнителните елементи върху дънната платка се ограничава до свързване на процесорната шина с относително несложния контролер на оперативната памет и още до свързването на тези два елемента към шината с общо предназначение, към която се подключват периферните потребителски компоненти. Типичен контролер на шината с общо предназначение е интегралната схема i8288. Вариантът на шината за компютърните системи IBM PC/XT (1981 година) се характеризира с това, че тя реализира 8-битов обмен на данни при 20 битов адрес. Тактовата последователност CLK в шината е 4,77[MHz]. Шината съдържа 4 линии за апаратни прекъсвания и 4 линии на заявки към каналите за пряк достъп до паметта. Архитектурата на компютърни системи с такава организация се определя като шинна. На фигура 5.5.3.2 обобщено е представена архитектурата на такава система.

Фиг. 5.5.3.2. Структура на система IBM PC/XT

Както може да се види, всички функционални единици, разположени върху дънната платка, са подключени към системната магистрала. Това означава, че всички контролери реализират системния интерфейс. Шината е синхронна и основният цикъл за обмен по нея се определя от цикъла на процесора. В този вариант най-често той е 4-тактен. Съществуват редица случаи, които се различават – имаме предвид циклите с изчакване, циклите на канала за пряк достъп до паметта и др. (вижте фигура 5.5.2.8 и фигура 5.5.2.9). Върху системната шина на дънната платка са реализирани 5 съединителни гнезда, предназначени за допълнителните контролери, като например този за управление на монитора. Тези гнезда представлява 62-контактни двустранни ножови съединители. Универсалният периферен интерфейс (УПИ), разположен върху дънната платка, е допълнен с необходимите логически схеми (ЛС) за подключване на клавиатурата и контролера на магнитна лента (СМТ). Максималната скорост на трансфер по тази шина се оценява на 4[MiB/s].

Ще обърнем внимание на тава, че системните шини се оценяват чрез три основни показателя: тактова честота на шината; разрядност на шината за данни и скорост на обмена. Скоростта на обмена по шината е функция от първите два показателя и се представя от произведението на честотата по разрядността. Така например, ако честотата на шината е 100[MHz], а разряднoстта е 32[b]=4[B], то теоретичната скорост за обмен е 400[MiB/s]. Производителността на шината може да бъде рязко повишена чрез практикуваното двойно увеличаване на ширината на данновата шина (8, 16, 32, 64 бита) или чрез увеличаване на тактовата честота. За съжаление и двата естествени подхода водят до непреодолими технически затруднения, свързани с изкривяване на сигналите и затруднено полагане на свързващите линии, което от своя страна води до усилване на влиянието на външни смущаващи фактори. За борба с изкривяванията се прилага снижаване на захранващото напрежение, което обаче засилва риска от случайни шумове. Ето защо при запазване на основните параметри на шината (тактова честота и ширина на данновата шина), производителността й се повишава чрез използване на диференциални тактови сигнали.

След първите образци на масово производство на персонални компютърни системи се появяват нови и подобрени такива, като например IBM PC/AT (през 1983 година). Реализирани са на базата на 16-битов микропроцесор i286. Масовото производство на отворени компютърни системи, към която политика се придържа IBM, изисква стандартизирана (общо приета) системна шина. Така се появява шината ISA (Industry Standard Architecture), разработена от IBM, в която има допълнителни 36-контактни двустранни ножови съединители. Така, заедно с онези от модела IBM PC/XT, стават общо 98=62+36. В IBM PC/AT архитектурата на входно-изходната система е приемник на предходния модел, но ширината на данновата шина е удвоена, тя е вече 16-битова. Ширината на адресната шина също е увеличена до 24 бита. Броят на линиите за заявки за апаратни прекъсвания става 15, а на линиите за заявки към каналите с пряк достъп до паметта – 7. Тактовата честота е повишена почти двойно – 8[MHz]. Максималната скорост на трансфер по тази шина се оценява на 16[MiB/s].

Създаването и масовото производство на нови микропроцесори продължава – появяват се моделите i386 (1985 година), i486 (1989 година). Това са вече много по-сложни 32-битови процесори. С тях започва постепенно усложняване на запомнящата система – върху дънната платка се появява кеш-памет, към която в последствие се добавя и вградена в процесора кеш-памет. Заедно с усложняването на логическата структура на процесорите се повишава и тактовата честота. Така вече ISA-шината става тясно място за тези системи. В края на 1988 година се появява нова системна шина EISA (Extended Industry Standard Architecture), разработена от международен консорциум от 9 фирми. Тя съдържа 32-битова адресна шина, 32-битова даннова шина, включително и за DMA-обмен. Тази шина е осигурена с усъвършенстван централизиран арбитраж и предлага средства за автоматична конфигурация. Системата за прекъсване също е подобрена и предлага за всяка IRQ-линия възможността за подключване на няколко еднотипни устройства. Освен това в тази шина продължава поддържането на съвместимост, т.е. произведените за ISA-шината контролери могат да работят и върху шина EISA. Запазена обаче е тактовата честота от 8[MHz]. Максималната скорост на трансфер по тази шина се оценява на 33[MiB/s].

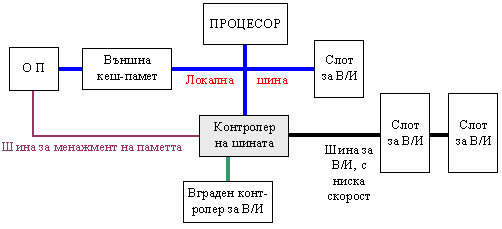

Микропроцесорите от това поколение изискваха по-големи скорости за трансфер с някои периферни устройства, особено тези, които обработват графична информация. Това доведе до добавяне в архитектурата на компютърните системи на втора шина, различна от системната. Тази шина беше едно продължение на процесорната шина и по тази причина се нарича локална. Така за първи път архитектурата на компютърните системи се изграждаше върху повече от една шина.

Фиг. 5.5.3.3. Дву-шинна архитектура (локална + шина за В/И)

Локалната шина беше специфицирана през 1992 година под наименованието VLB (VESA Local Bus). Към шината VLB се подключват видеоадаптери от тип VGA или SVGA, имащи повече цветове и по-голяма разделителна способност, контролери на бързи твърди дискове или мрежови контролери. VLB е шина за еднопроцесорни системи, върху която са допустими само 3 броя BusMaster-устройства. Тактовата честота на шината е стандартизирана в границите на 66[MHz], но спецификата на процесорните сигнали на практика я ограничава до 50[MHz]. При 32 бита ширина на данновата шина, реалната й трансферна скорост е 160[MiB/s]. Съществените ограничения обаче върху сигналите в тази шина, които комуникират непосредствено с процесора, както и някои недостатъци на този начин на подключване на периферни устройства, предопределят кратковременния живот на архитектурите с тази шина. С прекратяването на производството на микропроцесорите i486 тя окончателно остава в историята. Все пак разработването на тази шина се отчита като голяма стъпка в развитието на шинната архитектура на системите като цяло, тъй като се осъзнава възможността за многошинна организация на входно-изходната система.

Основен недостатък на компютърните системи с единствена шина представляват ограниченията, които тя създава при преследване на максималната пропускателна способност. Ако входно-изходният поток между устройствата трябва да преминава по централната шина, то такова ограничение рано или късно в еволюцията на системата тя ще създаде. Такива например са случаите, когато потребителят желае да подключи няколко нови устройства с високоскоростен обмен или иска да използва системата за управление на усилен трафик на комуникации. Традиционно шините се определят като шини за връзка на процесора с паметта и шини за вход-изход. Шините за вход-изход могат да имат по-голяма дължина, включително и под формата на кабели. Тези шини поддържат определен шинен стандарт, с което осигуряват подключването на различни по тип устройства. Шината за връзка на процесора с оперативната памет следва да осигурява максималната скорост на обмена, заложена в циклите на конкретния процесор и по тази причина е сравнително къса и непригодна за непосредствено подключване на други устройства. Онази шина, която се определя като локална, обединява процесора, буферните и логически схеми на различните линии и сигнали, паметта, както и контролера за връзка към системната шина. Последният представлява посредник към по-ниското шинно ниво (вижте фигура 5.5.2.14) и е наречен мост (bridge).

Разработването на шини, позволяващи достигането на висока производителност, показва, че три са възможностите за това:

· Разделяне на данновата от адресната шина, т.е. прилагане на принципа за еднофункционалност. Този принцип се отнася както за предназначението на линиите, така и за тяхната посока. Използването на една шина за предаване на данни в двете посоки я определя като полудуплексна. Когато за двете посоки се използват отделни шини, те се определят като дуплексни ;

· Повишаване на разрядността на данновата шина ;

· Прилагане на групов трансфер (блочен или пакетен режим на обмена).

Натовареността на дадена шина зависи от броя на главните (BusMaster) устройства. Процесорите (когато те са няколко) са винаги такива устройства. Както вече пояснихме в предидущия пункт, наличието на няколко главни устройства върху шината изисква наличието на арбитражна схема. Възможностите се основават на предварително присвоения приоритет или на по-справедливия случаен избор.

В настоящия момент се използват два типа шина, които се различават по начина на комутация:

1. Шини с комутация на връзките (circuit-switched bus) ;

2. Шини с комутация на пакетите (packet-switched bus).

Първият тип шини се характеризира с това, че когато едно главно устройство получи правото да управлява шината, то не я освобождава, докато не завърши транзакцията. При това по-голямата част от времето отива не за изпълнение на операцията, а в изчакване на естествената задръжка на по-бавното устройство.

Вторият тип шини осигуряват по-голяма пропускателна способност в сравнение с шините от първия тип. Това се постига чрез разделяне на транзакцията на две логически части – заявка за заемане на шината и отговор с трансфер. Този логика на обмена е получила наименованието split transaction (“разцепена” транзакция), а шината – наименованието конвейерна. Времето на латентността на по-бавното устройство, или може да се каже още времето, през което по-бавното устройство подготвя данните, се използва от другите “играчи”. Така инициаторът на операцията се бори да заеме шината за да заяви операцията, а изпълнителят се бори да заеме шината за да трасферира данните.

С появата на микропроцесор Pentium Pro и за всички следващи модели, за връзка с оперативната памет се използва отделна шина, която се нарича FSB (Front Side Bus). Тази шина осъществява трансфер при тактова честота от 100 или 133[MHz], което определя за нея скорост от 800[MB/s] нагоре. Тактовата честота на FSB-шината представлява един от основните параметри за възможностите на дънните платки.

Паралелно със споменатите

шини, през отминалия период се разработват и прилагат в различни компютърни

системи и други системни шини, цялото многообразие на които ние не сме в

състояние да изложим тук. По хода на изложението ще се спрем само на някои от

тях. Така например, една от най-прилаганите е споменаваната вече PCI-шина (Peripheral Component

Interconnect). Тя е предложена през 1992 година от Intel

като отворен стандарт за заинтересовани производители (PCI Special Interest

Group). Шината е 32-битова, при основна тактова честота 33[MHz]. Така

скоростта на трансфер е 132[MiB/s]. Същественото в концепцията на шината обаче е това, че тя е процесорно

независима. Това означава, че включената към нея периферия, може да

извършва обмен в различни платформи, с различни процесори - Pentium,

Alpha, R4400 и PowerPC. Освен това шината е проектирана в два варианта – като 32

и 64 битова и може да обслужва устройства със захранващи напрежения 5[v] и

3,3[v].

От началото през 1992 година, разпространението на PCI-шината е

масово. С времето тя е преработвана многократно. Известни са версиите PCI-2

(1993 година), PCI-2.1 (1995 година), PCI-Х (1999 година), PCI Express.

Последната започва да се разработва от 2003 година от компаниите Intel, Dell, HP и IBM, минавайки през стандарти

от 1.0, 2.0, 3.0 ... до 6.0 към настоящия момент (2020 година). Читателят

навярно разбира, че този процес няма да завърши с тези разработки. Общите

принципи обаче вече са оформени и ние следва да ги поясним, а това ще бъде една

добра основа на читателя за бързото усвояване на следващите версии. Еволюцията

на тази основна шина, както и на нейните технически параметри, към настоящия

момент читателят може да проследи по следните адреси:

https://en.wikipedia.org/wiki/PCI_Express

https://en.wikipedia.org/wiki/PCI_Express#PCI_Express_6.0

Заедно с тази шина са добили популярност още много други.

Показателна е съдбата на някои от тях. Така например изоставането на PCI-шината

в някои показатели е било причина за поява на AGP-шината (AGP - Accelerated Graphics Port), с варианти AGP-х1 от 1996 година

и AGP-х2 от 1998 година и др. AGP-шината се реализира в единствен съединител на

дънната платка и за нея са показателни следните параметри:

Таблица

5.5.3.1 Ускорен графичен обмен

|

Означение на шината |

Захранване |

Тактова честота |

Скорост на трансфер |

|

AGP x1

(предава 1 бит на такт) |

3,3 [v] |

66 [MHz] |

266 [MiB/s] |

|

AGP x2

(предава 2 бита на такт) |

1,5 / 3,3 [v] |

66 [MHz] |

533 [MiB/s] |

|

AGP x4

(предава 4 бита на такт) |

1,5 [v] |

66 [MHz] |

1,066 [GiB/s] |

|

AGP x8

(предава 8 бита на такт) |

0,8 / 1,5 [v] |

66 [MHz] |

2,133 [GiB/s] |

Тази шина от своя страна обаче отстъпва място на PCI Express.

Често авторите наричат шините стандартни. Това

определение обаче се нуждае от пояснение. Обикновено броят и типът на

устройствата за вход-изход в предлаганите на пазара компютърни системи не е

фиксиран. Това позволява на потребителя сам да съставя необходимата му

конфигурация. Шините за вход-изход и съединителните гнезда върху тях можем да

разглеждаме като шини за разширения към системата. Ето защо стандартите в това

направление играят важна роля, позволявайки на проектантите на компютърни

системи да работят независимо от тези на входно-изходни устройства. Появяването

на стандартите се определя от различни обстоятелства. Понякога широкото

разпространение и общото признание на една разработка я налага фактически като

стандарт. Такъв е случаят с ISA-шината. Имало е случаи, когато като стандарт се

узаконява в резултат на високи достижения в сектора на пазара на периферни

устройства. Такъв е случаят с Ethernet. Успехът на даден стандарт в тази област в значителна степен се

определя от това, дали такива влиятелни организации, като ANSI (Национален

институт по стандартизация на США) или IEEE (Институт на инженерите по

електротехника и радиоелектроника), го оценяват положително и го

препоръчват. Понякога стандарт за компютърна шина е бил предлаган и от някой от

комитетите по стандартизация. Пример за такъв случай е шината, наречена FutureBus

– асинхронна процесорно независима шина, предложена от IEEE.

В системи на базата на микропроцесори SPARC

се използват няколко вида шини. Като шина за вход-изход се използва шината SBus

(стандарт IEEE-1496), а за обединяване на множество процесори и памет се

използват шините MBus и XDBus. Първата от тях (SBus) има два варианта на

трансфер – 32 и 64-битова реализация при тактова честота до 25[MHz]. Шината

реализира два метода за обмен – PIO (програмируем вход-изход) и DVMA (пряк

достъп до виртуалната памет). Шината MBus е 64-битова и работи с тактова

честота 50[MHz] в синхронен режим с мултиплексиране на адреса и данните. Шината

е проектирана за малки разстояния и има контролер, който поддържа

кохерентността на кеш-паметта в системи, имащи до 4 процесора (проблемът

кохерентност е разгледан в глава 6). За системи с повече процесори е

предназначена третата шина – XDBus. В системите SPARCcenter 2000 тя поддържа до

20 процесора, а в системите SuperServer 6400 - до 64 процесора.

В някои съвременни компютърни системи се използват фирмени

(патентовани) шини. Типичен пример е системната шина POWERpath-2

на компанията Silicon Graphics.

Една от най-популярните шини е означена SCSI (Small Computer System Interface) и представлява набор от стандарти и определящи механизми за реализация на магистрали за обмен между процесора и периферните устройства, разработени от ANSI – Националния институт по стандарти на САЩ. Разработени са три стандарта SCSI-1 (X3.131 от 1986 година), SCSI-2 (X3.131 от 1994 година) и SCSI-3 (X3.270 от 1996 година). Главна особеност на тази шина е изискването за “интелигентен” контролер в периферното устройство. Постигането на висока степен на независимост спрямо разнообразните периферни устройства, в операционната система SCSI-устройствата се представят с проста линейна структура от еднакви по обем последователни блокове. Тази структура следва да се разпознава и преобразува в права и обратна посока от контролера на периферното устройство. За свързване е предвиден 50-жилен кабел. В стандарта SCSI-2 се различават различни режими: Wide SCSI, Fast SCSI и Fast-and-Wide SCSI. Режимът Fast SCSI разполага с 8 битова даннова шина и тактова честота 10[MHz]. Режимът Wide SCSI разполага с двойно или четворно по-широка даннова шина (16 или 32 бита) и тактова честота 5[MHz]. При същата честота комбинацията Fast-and-Wide SCSI достига скорост на трансфер 20 и 40[MiB/s] съответно. За реализация на този комбиниран режим обаче е предвиден друг 66-жилен кабел, наречен В-кабел. Широкото използване на твърди дискове със скорост на въртене 7200 оборота за минута направиха тази технология много актуална.

SCSI-2 поддържа до 16 устройства включени на един кабел. Предаването е паралелно 16 битово. Означението SCSI-3 представлява набор от стандарти, с което се цели по-лесна актуализация на стандартите за бързо изменящи се технологически области. Крайната архитектура (ANSI X3.270) от 1996 година е известна още под наименованието SAM (SCSI-3 Architecture Model). Шината остава 16 битова, но скоростта е повишена до 320[MiB/s]. Това се дължи на използването на връзка с оптични влакна (Fiber Channel SCSI), с която последователно могат да се подключват до 126 устройства. Връзката е способна да поддържа скорост от 2[GiB/s] на разстояние няколко километра. Тази последна версия на стандарта използва за 16 битовата шина 80 жилен кабел. Разработено е съединение за безопасно “горещо” подключване на устройства, работещи в система RAID (разширен масив от независими дискове).

Конкурент на шината SCSI е Serial ATA (SATA). Разликата в последната се състои в това, че тя прилага паралелния IDE-интерфейс с диференциален тактов сигнал. Така при същата ширина на кабела се повишава производителността, като превишава с 30% тази на Parallel ATA (PATA).

Видове

входно-изходна архитектура

Архитектурата на дънните или още на системните платки се

развива главно под влиянието на концепциите за входно-изходен обмен в

процесорните схеми от една страна и на концепциите за входно-изходен обмен в

периферните системи от друга страна. Разновидностите са три и често взаимно се

припокриват:

1.

Шинно-мостова архитектура ;

2.

Хъбова архитектура ;

3.

Архитектура “HyperTransport” (HT) – може да бъде определена като тунелна.

Исторически, както вече кратко описахме, първоначално се развива шинно-мостовата архитектура. Като нейни алтернативи по-късно се явяват хъбовата архитектура и архитектурата НТ. Системното проектиране на архитектурата на една компютърна система следва да бъде независимо от физическите съединения върху системната платка и физическата реализация на периферните устройства. Това е необходимо и за системното разработване на програмното осигуряване. Ето защо всички нейни елементи се представят като логически (устройства или функции). Така в много от интерфейсите се използва подход за разпределение на системните ресурси и се говори за конфигурация.

Следващият

раздел е:

5.5.3.1 Шинно-мостова архитектура

на входно-изходната система