Последната актуализация на този раздел е от 2020 година.

5.5.2 Канал за пряк

достъп до паметта (DMA).

Шинно-мостова организация на системата за вход-изход – Продължение

1

Апаратно управляван входно-изходен

обмен

Когато става дума за обмен с бавнодействащи устройства, като клавиатури, печатащи устройства, монитори и др. има смисъл да се осъществява прекъсване на процесора за предаване на всяка порция данни, която може да се предаде по данновата шина за един цикъл. Но когато става дума за бързодействащи устройства, в които порцията от данни има значително по-голям обем, примерно от 128 до 2048 и повече байта, ситуацията се изменя по същество. Информационната единица върху носителя на външни устройства от този тип, каквито са например дисковите запомнящи устройства, се нарича блок и има споменатия по-горе размер. Размерът на блока се определя от конструкцията на външното устройство и не може да се променя от програмиста. Така при обмен с такива устройства основната порция данни е блокът.

За да се осъществи по програмен път предаване на един блок между външно устройство и оперативната памет, програмата би трябвало след иницииране на операцията да изчака превъртането на носителя, докато под главите за четене/запис от носителя попадне началото на необходимия блок. Времето за очакване на това събитие (или времето за достъп) при работа с дискови устройства обикновено се движи в интервала от 8 до 250[ms]. Като се имат предвид високите честоти, с които работят съвременните процесори, най-целесъобразно е това събитие да се сигнализира чрез прекъсване на процесора.

По-нататък в процедурата за входно-изходен обмен следва предаване по данновата шина на отделните думи от блока в непрекъсната последователност до неговото изчерпване. Известно е например, че в запомнящото устройство с гъвкав магнитен диск с единична плътност, скоростта за четене/запис върху носителя се измерва на 31,25[KiB/s], което означава, че отделните байтове от блока следват през 32 микросекунди. В същото време при двойна плътност скоростта нараства до 62,5[KiB/s], т.е. 16 микросекунди на всеки байт. За сравнение, скоростта на предаване в типична съвременна DDR2 памет, е 400[MiT/s], което означава 2,5[ns] за един трансфер. А при най-новите памети (вижте глава 4) скоростите са още по-високи и достигат примерно до 6400[MiT/s]. При това съотношение е малко вероятно, че една програма за обслужване на прекъсване ще успява да изпълни необходимите действия за предаване на текущия байт (порция) данни, до пристигане на следващия.

Читателят навярно разбира, че проблемът на програмно управлявания обмен е, че е на границата на възможностите си. В случай, че трябва да се работи с "твърд" диск, където всеки нов байт се появява на всеки 8 миросекунди и дори по-малко, като имаме предвид съвременните твърдотелни SSD дискове, този метод става неприложим.

Скорост за предаване на данни в някои типични устройства

|

Устройство |

Скорост

на обмен |

|

Клавиатура |

10 [B/s] |

|

Мишка |

100 [B/s] |

|

Модем 56K |

7 [KiB/s] |

|

Скенер 300 dpi |

1 [MiB/s] |

|

Цифрова камера |

3,5 [MiB/s] |

|

Blu-ray диск – 4x |

18 [MiB/s] |

|

Безжична мрежа 802.11n |

37,5 [MiB/s] |

|

USB 2.0 |

60 [MiB/s] |

|

FireWire 800

(IEEE 1394) |

100 [MiB/s] |

|

Gigabit Ethernet мрежа |

125 [MiB/s] |

|

Диск SATA 3 |

600 [MiB/s] |

|

USB 3.0 |

625 [MiB/s] |

|

Диск SCSI Ultra-5 |

640 [MiB/s] |

|

Една линия в шина PCIe 3.0 |

985 [MiB/s] |

|

Samsung SSD

950 PRO M2 |

2500 [MiB/s] |

|

Шина Thunderbolt-2 |

2,5 [GiB/s] |

|

Мрежа SONET OC-768 |

5 [GiB/s] |

В този случай се говори, че пропускателната възможност на процесора е недостатъчна или още, че скоростта за предаване се ограничава от процесора. Ето защо, за обслужване на В/И обмен с бързодействащи външни устройства се прилага апаратно управление. Апаратурата която реализира това управление представлява канала за пряк достъп до паметта (КПДП).

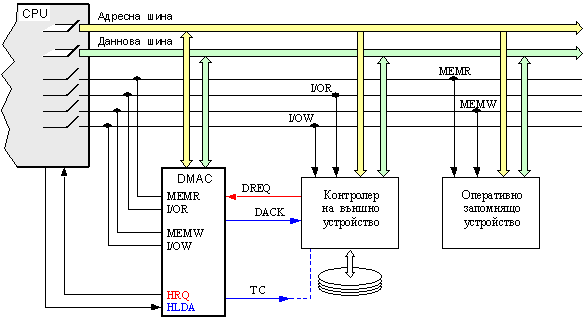

Обикновено интерфейсът за връзка с основната памет се управлява от процесора, който осигурява предаването на данни с необходимия адрес и последователност от управляващи сигнали. В случая, описан по-горе, се налага тези функции временно да се поемат от канала за ПДП. Това най-общо означава, че когато настъпи моментът на обмен, процесорът трябва да бъде спрян и изолиран от шините, като подаването на адресите и на управляващите сигнали по шината за връзка с паметта, ще бъдат осигурявани от канала за ПДП. Необходимата за тази цел апаратура се оформяла първоначално конструктивно във вид на самостоятелен елемент (интегрална схема) и се нарича контролер за пряк достъп до паметта (КПДП) – DMA (Direct Memory Access Controller). В съвременните архитектури, благодарение на новите производствени технологии, тя е вече включена в съставна част на други интегрални елементи на компютърните системи, но нейната същност не се променила, ето защо ще я поясним на базата на система с непосредствени връзки. Мястото на КПДП в системата за вход-изход с такава системна шина е показано на фигура 5.5.2.9.

Фиг. 5.5.2.9. Структура на входно-изходна система с КПДП от тип i8237

Вече беше споменато, че входно-изходната система може да бъде осигурена с допълнителна даннова шина и дори с допълнителна даннова шина само за каналите с пряк достъп до паметта. Следвайки тази логика можем да проследим еволюцията на компютърните системи до съвременните разклонени йерархични интерфейсни системи за връзка на разнообразни входно-изходните устройства с процесора. Що се отнася до принципите по които са реализират такива системи, те не се отличават от изложените тук.

И така, след като вече бе изяснена организацията на прекъсване и организацията на входно-изходния обмен чрез прекъсване, не е трудно да се обясни апаратната реализация на входно-изходната операция. Основната функция на КПДП е да замести процесора при непосредственото изпълнение на машинни команди от вида "Въведи" или "Изведи", като за целта изработва необходимите адреси за оперативната памет и необходимите управляващи сигнали. Този контролер може да се намира в две състояния – в неактивно (пасивно) състояние, когато към него не се подават заявки за обслужване и в активно състояние, в което преминава след получаване на заявка за обслужване на обмен от непосредствено свързано към него устройство.

По-подробно алгоритъмът на входно-изходната операция, в условията на структурата от фигура 5.5.2.9, представлява следната последователност:

1. Когато контролерът на външното устройство формира в съответния даннов буфер (за въвеждане или за извеждане) текущата порция данни и достигне момента на готовност, той изработва сигнала DREQ (заявка за обмен на готови данни). Този управляващ сигнал се подава по специална линия към контролера за пряк достъп до паметта (КПДП).

2. След като КПДП получи тази заявка, той поема инициативата да я обслужи, а контролерът на външното устройство през това време остава в състояние на очакване. Инициативата на КПДП се изразява в това, че той подава към процесора (или към арбитъра на системната шина, който е част от системата за прекъсване на процесора), сигнал HRQ (заявка за заемане на системната шина).

3. Поради високите скоростни изисквания, реакцията на процесора на тази заявка трябва да бъде възможно най-бърза. Неговата работа трябва да бъде прекъсната, но едно прекъсване, осъществено в смисъла на микропрограмната процедура за осъществяване на прекъсването (МППОП) в случая, е неприложимо. То е неприложимо, тъй като е много бавно в следствие на многократните обръщения към програмния стек при запис на текущото състояние на процесора. Прекъсването на процесора при заявка от страна на КПДП следва да се разбира и реализира по съвършено различен начин, а именно като буквално спиране на превключванията. Това спиране обаче трябва да позволява и следващо пускане, при това от същото алгоритмично място. Такова спиране е възможно да се реализира единствено чрез затваряне на достъпа на тактови импулси към управляващото устройство на процесора и прекъсване на микропрограмно ниво. В отговор на заявката HRQ на КПДП, постъпила на специално предназначен за целта вход в процесора, последният се самоизключва от системната шина и издава уведомяващия за това събитие сигнал HLDA, обратно към КПДП. Това става в продължение на един такт на шинния синхросигнал CLK. Така КПДП получава правото да управлява шината.

4. След получаване на потвърждението HLDA, контролерът за пряк достъп до паметта (КПДП) изпълнява алгоритъма на процедурата за обмен, вградена в неговото управляващо устройство. Последното използува същите тактови импулси, които се разпространяват по системната шина CLK, с което не се губи синхронизацията между ползвателите на шината. Първото което прави КПДП е да уведоми контролера на външното устройство, че е получил правото да управлява обмена, като му изпраща потвърждаващия сигнал DACK по специалната линия, с която са свързани.

Сигналът DACK се интерпретира в контролера на външното устройство като разрешение за предаване на данни - контролерът подключва съответния даннов регистър към системната шина.

Едновременно с това КПДП подава необходимия адрес на адресната шина и в съответната последователност генерира и двойките управляващи сигнали (I/O_R, MEM_W) при операция "Въвеждане" или (MEM_R, I/O_W) - при операция "Извеждане".

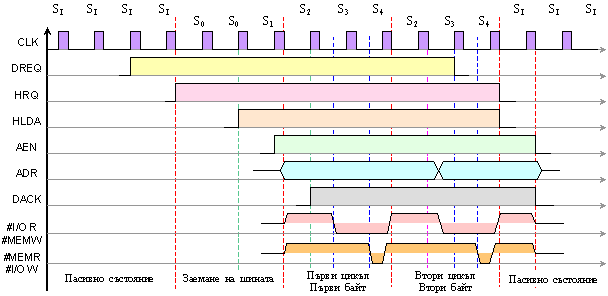

Така във времето след сигнала DACK се развива входно-изходната операция, което е изразено с времедиаграмата от фигура 5.5.2.10.

5. След като предаването на данните между клетката от оперативната памет и данновия регистър на контролера на външното устройство завърши, КПДП дезактивира сигналите DACK и HRQ и изключва своите шини от системните, с което както процесорът, така и контролерът на външното устройство, получават разрешение за самостоятелна работа. С отпадането на заявката HRQ процесорът възстановява своята работа.

В същото време КПДП актуализира своето вътрешно състояние. Актуализацията означава, че КПДП формира следващия адрес на клетка от ОП в специален адресен регистър, изпълнен като брояч. Освен това извършва отброяване на текущото предаване на данни в отделен брояч. Чрез този брояч КПДП проверява условието за край на предаващият се в момента блок от данни.

Докато КПДП актуализира вътрешните си регистри, контролерът на външното устройство работи с външното устройство и подготвя следващата порция данни (байт, дума или друга по обем порция). Когато тя се запише в данновия регистър при въвеждане, или когато тя се запише върху носителя и освободи регистъра за извеждане, контролерът на външното устройство преминава в състояние на готовност.

От този момент нататък операцията се повтаря, след като контролерът на външното устройство издаде заявката за обслужване DREQ.

Ако външното устройство не снеме заявката DREQ след получаване на потвърждението от КПДП, това означава, че то се намира в режим на обмен на блок и докато не предаде всички порции от блока няма да снеме заявката за обслужване. Естествено, КПДП също няма да освободи шината, докато сигналът DREQ е активен.

Фиг. 5.5.2.10. Входно-изходен обмен с КПДП при предаване на две порции данни

Ако текущото предаване на порцията данни обаче е било последното, което се разбира по това, че контролният брояч в КПДП се е нулирал, КПДП сигнализира за край на предаването. За целта в байта на състоянието му се установява флаг за превъртане на брояча (край на блока). Освен този флаг, за бързо уведомяване на процесора, както и на външните устройства за това събитие, КПДП генерира още един специален сигнал ТС (Terminal Count - превъртане на брояча).

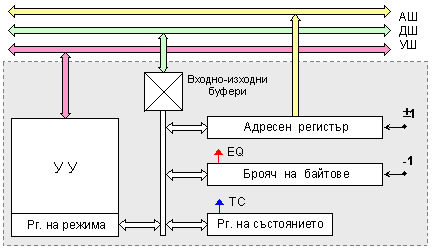

От казаното може да се почувствува в най-общ план вътрешната логическа структура на КПДП. Ясно е, че преди началото на обмена тази логическа структура следва да бъде инициализирана (програмирана) като бъдат зададени началните стойности на съответните логически възли. На фигура 5.5.2.11 е показан примерният състав на логическата структурата на КПДП. В предложената структура за управление на процеса на обмен е реализирано управляващо устройство (УУ), което изпълнява основния алгоритъм с необходимата модификация, в зависимост от съдържанието на регистъра на режима, в който основната информация е кодът на заявената от процесора входно-изходна операция - въвеждане или извеждане.

Фиг. 5.5.2.11. Структура на канала за пряк достъп до паметта (програмен модел)

В реалните КПДП се реализират разнообразни режими: режим на единичен обмен, режим на блоков обмен, обмен от тип памет/памет и др. В последния случай стават възможни за реализация машинни команди от тип "Копиране", "Сравнение на масиви" и др.

При програмиране (инициализиране) на логическата структура на КПДП, в регистъра на режима се установява точно определена константа, съответстваща на избрания режим за обмен. Освен този регистър, начално съдържание получават всички програмно достъпни регистри и преди всичко адресният регистър (реверсивен), в който се записва началния адрес на областта от оперативната памет, която ще участвува в обмена, както и брояча на порции (байтове), който се зарежда с общия брой данни (минус единица). Записът е резултат от инициализиращата програма, изпълнявана в процесора преди началото на обмена. За тази цел програмно достъпните регистри на КПДП имат точно определени фиксирани адреси във входно-изходното адресното пространство (вижте разпределението на входно-изходното адресно пространство в предидущия пункт 5.5.1). В структурата от фигура 5.5.2.11 по-горе умишлено са пропуснати входната адресна шина и адресните дешифратори, формиращи разрешаващите сигнали към програмно достъпните възли.

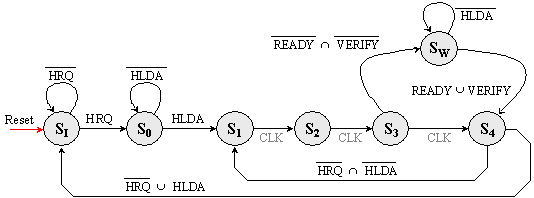

Както се вижда в структурата, модификацията на адресния регистър и брояча на порциите е функция на управляващото устройство. Последното работи в съответствие със следния граф на превключванията:

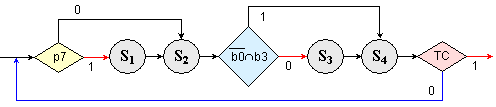

Фиг. 5.5.2.12. Граф на състоянията на КПДП

В управляващия автомат на КПДП са реализирани различни режими за работа на каналите, които се управляват от съдържанието на регистъра на режима. Така например, когато каналът за пряк достъп до паметта е програмиран за работа в блочен режим (битове b7,b6 в регистъра на режима имат стойностите b7=1, b6=0 ), трансферът на заявеното количество отчети се извършва чрез непрекъснато следващи цикли на обмен, инициирани от една единствена заявка. Веднъж заел системната шина контролерът (КПДП) не я освобождава докато не се формира флагът ТС (Terminal count). При този начин на работа (непрекъснато следващи чисти цикли на обмен) КПДП разчита, че източникът на данни е винаги готов за четене. На фигурата по-долу е представена тази част от графа на състоянията му при работа в блочен режим.

Фиг. 5.5.2.13. Граф на цикъл за блочен обмен в канал за пряк достъп до паметта

От фигурата се вижда, че ако не е

изпълнено условието за край на цикъла за трансфер, т.е. когато ТС=0, КПДП преминава последователно

през четири състояния (S1, S2, S3, S4), при което издава необходимите

управляващи сигнали към процесора, към паметта и към външното устройство. Но не

във всеки цикъл тези състояния присъстват едновременно. Обикновено преносът от

осмия разряд на адреса е нула (р7=0), което означава, че при нормална (некомпресирана)

времедиаграма, се редуват състоянията (S2, S3, S4), (S2, S3, S4) ... .

Некомпресирана времедиаграма се изпълнява, когато битовете b0 и b3 в

управляващия регистър на КПДП образуват конюнкцията: ![]() . На всеки 256 такива цикъла възниква преносът р7 (р7=1) и тогава се извършва преход

и през състояние S1, т.е. редуването е следното: ... (S2, S3, S4), (S1, S2, S3,

S4), (S2, S3, S4), ... . Така тези цикли са с един такт на сигнала CLK по-къси,

в резултат на което този режим получава допълнително ускорение при обмен на

данни.

. На всеки 256 такива цикъла възниква преносът р7 (р7=1) и тогава се извършва преход

и през състояние S1, т.е. редуването е следното: ... (S2, S3, S4), (S1, S2, S3,

S4), (S2, S3, S4), ... . Така тези цикли са с един такт на сигнала CLK по-къси,

в резултат на което този режим получава допълнително ускорение при обмен на

данни.

Когато каналът за пряк

достъп е програмиран да реализира компресирана времедиаграма, т.е. при

условието (![]() ), то от циклите на обмен се изключва състояние S3. Тогава

КПДП изпълнява своите цикли като преминава само през състояния S2 и S4, към

които на всеки 256 повторения включва и състояние S1. Така типичното време на

машинния цикъл се формира само от два машинни такта. Естествено този режим на

КПДП следва да бъде възможен и за външното устройство, което подава или приема

порции данни в същия темп.

), то от циклите на обмен се изключва състояние S3. Тогава

КПДП изпълнява своите цикли като преминава само през състояния S2 и S4, към

които на всеки 256 повторения включва и състояние S1. Така типичното време на

машинния цикъл се формира само от два машинни такта. Естествено този режим на

КПДП следва да бъде възможен и за външното устройство, което подава или приема

порции данни в същия темп.

На практика, когато КПДП е затворен в корпуса на една интегрална схема, под негово общо управление се намира апаратното оборудване поне на 4 канала за пряк достъп до паметта, свързани в низходящ ред на приоритета. Това позволява каскадно свързване на схемите, с което може да се построи достатъчно богата и развита система от канали за ПДП.

Концепцията за апаратно управление на входно-изходния обмен в лицето на каналите за пряк достъп до паметта е извървяла дълъг еволюционен път заедно еволюцията на технологиите и непрекъснато нарастващите скорости на обмен. С появата на стандарта на разширената системна шина EISA скоростите за обмен чрез ПДП достигат 33[MiB/s]. Възможностите на КПДП са увеличени, въведени са допълнително високо производителни режими. Особена роля при повишаване на трансферната скорост оказват повишената тактова честота на шината и повишената разрядност на данновата магистрала.

Над 90% PC-системите са оборудвани с твърди дискове имащи интерфейс IDE (Integrated Device Electronic), което го прави най-разпространения интерфейс за свързване на твърди дискове. Към тях могат да се добавят и CD, CD-R, CD-RW и DVD устройствата. През 1984 година, смятана за година на раждането на интерфейса IDE, след като IBM произведе своят модел АТ (Advanced Technology), Western Digital реализира идеята контролерът, използващ ISA шината да бъде интегриран в твърдия диск. Така се появява интерфейсът АТА (AT Attachement - прикрепване), който впоследствие става известен под името IDE. Интерфейсът и до днес е 16 битов. Стандартът на ANSI специфицира АТА със следните възможности:

· Поддръжка на два диска върху един канал (master & slave) ;

· PIO modes - 0,1,2 ;

· DМА modes - single word DMA modes 0,1,2 ;

· Multiword DMA mode 0 .

Не след дълго, вследствие на потребности от по-високи скорости за предаване на данни от ANSI е бил стандартизиран нов, съвместим с АТА интерфейс, наречен АТА-2, който добавя към гореизброените възможности, нови:

· PIO modes - 3, 4 ;

· DMA modes - multiword DMA modes 1, 2 ;

· Block transfer ;

· LBA (logical block adressing) .

Предложен за стандартизиране е още АТА-3, съдържащ средства за повишаване на надеждността на данните. Той не е бил стандартизиран поради факта, че не съдържа нови режими. На смяна на АТА-3 се яви стандартът Ultra ATA. Този стандарт добави поддръжката на DMA mode 3, позволяващ пренос на данни със скорост до 33,3[MiB/s]. При този стандарт за осигуряване на предаването на данните по 40 - контактния 40 - жилен лентов кабел се използват специални схеми за контрол и корекция на грешките. Следващото ниво е Ultra ATA-66, позволяващ предаването на данни със скорост до 66[MiB/s], като предаването на данни вече се извършва по 80-жилен 40-контактов кабел. Следва интерфейсът Ultra ATA-100 – скорост за трансфер 100[MiB/s].

От 2002 година в разпространение влиза следващият стандарт - Serial ATA. При него скоростта на обмен достига 150[MiB/s]. С това развитието не спира – следва удвояване и учетвoряване на скоростта.С масовото използване на PCI-стандарта за системната шина и увеличаване на броя на производителите на компютърно оборудване, централизираното управление на апаратно управлявания входно-изходен обмен премина в разпределено. В резултат се появява например механизмът DDMA (Distributed Direct Memory Access), при използването на който производителите вграждат контролер за пряк достъп до паметта, като средство за управление на обмена, в периферните PCI-контролери.

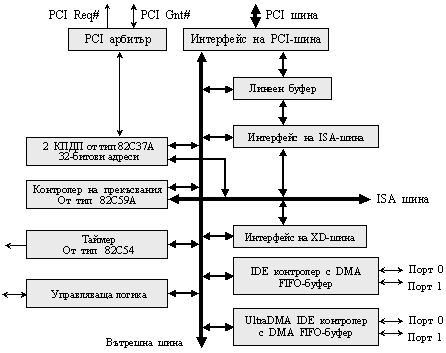

Типичен пример за развитие и интегриране на устройствата за управление на входно-изходните операции са интегралните схеми, свързващи към процесора различни шини, като например системни контролери за вход-изход, които често се наричат кратко шинен мост, или още шинен съгласовтел. Различни фирми произвеждат такива схеми, които успешно се използват като PCI-мост от стандартна ISA-шина. В структурата на една такава схема могат да се съдържат два КПДП от описания по-горе тип. Тези контролери могат да управляват по 4 32-битови канала. Съгласуването с 8 и 16-битовия ISA-обмен се постига чрез добавените в структурата на тези контролери 4-байтови буфери. В структурата на подобна интегрална схема се съдържат още IDE-контролери, контролер за прекъсване, BIOS-таймер, няколко програмируеми таймери, както и пълния комплект логически схеми на PCI-интерфейса. IDE-контролерите осигуряват конвейерен трансфер на 16 или 32-битови данни. С цел да се избегнат тактове на изчакване върху PCI-шината, те съдържат DMA FIFO-буфери с обем до 64 байта. В управлението на този буфер се прилага алгоритъм с изпреварващо четене и задържан запис. Циклите на четене и на запис върху PCI-шината се изпълняват до тогава, докато буферът с изпреварващо четене на се запълни или буферът със задържан запис не се освободи. На следващата фигура е представена обобщената вътрешна структура на подобна схема.

Фиг. 5.5.2.14. Структура на типичен PCI-мост към ISA-шина

Представената структура съдържа още необходимия интерфейс към XD-шина, която се използва при реализация на системи с няколко процесора. Такива са например сървърните системи SPARCcenter 2000 на компанията Sun Microsystems, които могат да съдържат до 20 процесора и още системата SuperServer 6400 (до 64 процесора) на компанията Cray Research. XD-шината работи в режим наречен разцепена транзакция и поддържа производителност от 310[MiB/s], като може да достигне пиковата стойност от 400[MiB/s]. Задачите и възможностите на подобни схеми ще представим по-късно.

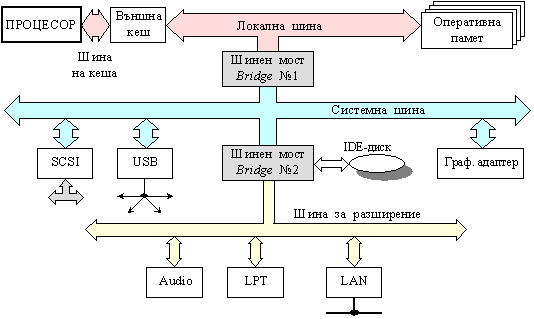

Съвременните РС-платформи имат йерархична система от различни входно-изходни шини (магистрали). Типичен пример е платформа с три нива, които се определят от: локалната шина на процесора (Local Bus); от системната шина (System Bus); и от шината за разширение (Expansion Bus). Така структурата на типичната РС-система може да се изобрази по следния начин:

Фиг. 5.5.2.15. Йерархия на връзките в РС-система

В показаната структура трансферът между отделните нива се осигурява от съответните контролери в шинните мостове. Така например контролерът за управление на оперативната памет свързва процесора и кеш-паметта чрез локалната шина, но в същото време апаратурата в този мост може да свърже оперативната памет с външно устройство, подключено към системната шина, като по този начин избягва участието на процесора в обмена. Вторият шиннен мост създава по-голяма гъвкавост в системата, като разделя информационните потоци между процесора и оперативната памет от тези между оперативната памет и входно-изходните контролери. Контролерите на интерфейсите SCSI и USB свързват към системната шина локални дискове и постоянна памет. Към шината за разширение се включват още Ethernet-адаптери и комуникационните адаптери COM. Изключително популярни са наименованията на шинните мостове – “северен мост” (North Bridge)и “южен мост” (South Bridge). Наименованията произлизат от вида на рисунката, в която обикновено системната шина е изобразена хоризонтално в средата на чертежа, наподобявайки екватора, над който е изобразен “северният мост” за връзка с процесора, а отдолу е изобразен “южният мост”, за връзка с разширенията на системата. Като цяло архитектурата на подобни системи се нарича шинно мостова. Наборът от интегрални схеми за реализация на входно-изходната система се нарича чипсет (набор от чипове).

Следващият

раздел е:

5.5.2 Метастабилност.

Арбитриране. Арбитър – Продължение 2