Последната

актуализация

на този

раздел е от 2020

година.

5.4.4

Векторна

система за

прекъсване

Както

вече беше

изяснено,

най-съществените

качества на

една система

за

прекъсване са

постигане на

високо

бързодействие

на прехода и

осигуряване

на минимален ангажимент

от страна на

процесора

при избора на

заявка за

прекъсване.

Не

по-маловажно

качество е

възможността

за

управление на

системата за

прекъсване.

Реалните

ситуации са

твърде

разнообразни

и

комплицирани

и

възможността

за

управлението

им е твърде

желана.

В

сравнение с

вече

изложените

подходи значително

по-голяма

гъвкавост,

свобода и бързодействие

предлага

така

наречената векторна

система за

прекъсване.

Векторната

система за

прекъсване

се основава

на идеи,

които

частично

вече бяха

представени.

За да се облекчи

процесорът,

се приема

уговорката, че

всяка заявка

за

прекъсване

ще се съпровожда

и от адреса

за преход към

обслужващата

програма, или

от

информация и

функционалност

за неговото

изчисляване.

Адресът за преход

към

обслужващата

програма се

нарича вектор.

Векторите за

прекъсване

се

съхраняват в

таблица

(масив в

паметта),

достъпът в

която се

осигурява от

апаратурата

на системата

за

прекъсване и

адресиращото

устройство в процесора.

Основният

вид на

функционалността

за достъп

беше

представена

с изразите

(5.4.2.1) ¸ (5.4.2.4). Според

тази

функционалност,

адресът за преход

АПР към

обслужващата

програма се

извлича от таблицата

с векторите

за

прекъсване,

по адрес,

който се

формира

апаратно от

номера V на

приетата

заявка. Във

всички

случаи обаче

адресът за

преход се

осигурява

поне след

едно

обръщение към

паметта.

При тази постановка задачата за избор на ЗП може да бъде решена с чисто апаратни средства. Нещо повече, в логиката за избор могат да бъдат въведени допълнителни възможности за апаратно и програмно управление на приоритета.

Забраната

за

прекъсване

по време на

обслужване

на вече

приета

заявка, която

налага МППОП,

а така също и

програмата "Полинг", не

предполага

възможността

за реализация

на вложени

прекъсвания.

Отлагането

на обслужването

чрез

маскиране или

чрез дълбоко

влагане на

прекъсванията

може да

доведе до

загуба на

заявки от

бързодействуващи,

високопроизводителни

устройства,

които могат

да се появят

по време на обслужването

на

устройство с

по-нисък приоритет.

За да се

предотврати

тази

ситуация и за

да се осигури

възможно

най-бързата

реакция на

процесора, е

необходимо

да се решат

две задачи:

а)

Възможно

най-бързо да

се осъществи

избор на ЗП

според

текущия

приоритет;

б)

Да се направи

възможно

управлението

на приоритета

на текущо

изпълняваната

програма.

Поставените

задачи по

същество

целят обслужването

на

прекъсванията

да позволява ниво

на вложеност

по-голямо от

единица, т.е.

прието за

обслужване

прекъсване

да може да се

прекъсва от

по-приоритетно,

аналогично

на

възможностите

на

подпрограмната

техника. За

постигане на

тези

възможности

се въвеждат

понятията ниво на

текущия

приоритет и маска на

програмата, а

апаратурата,

необходима

за

реализация на

описаната

възможност,

се обединява

в устройство,

което се

нарича програмируем

контролер на

прекъсванията

или просто

контролер на

прекъсванията.

Контролерът

се нарича

програмируем,

тъй като дава

възможност

на

програмиста

да назначава за

неговите

характеристики

различни стойности

и да определя

различни

режими за работа,

които

най-точно

съответстват

на външното

обкръжение и

характера на

изчислителния

процес във

всеки един

момент.

Нивото

на текущия

приоритет

следва да се

разбира като

цяло число в

интервала [0,255].

Това число

сравнява

приоритета

на всяка постъпила

заявка за

прекъсване и

се явява като

бариера по

пътя й към

процесора.

Отношението

е такова, че

заявката

остава зад

бариерата,

ако нейният приоритет

е по-нисък от

установения,

т.е. от бариерата.

Вдигайки или

сваляйки

нивото на текущия

приоритет,

програмистът

може да селектира

заявките в

полезрението

на процесора.

Програмните

маски са

еднобитови

стойности,

пряко

съответстващи

на всеки вход

за ЗП.

Отношението

на маските е

разбира се

конюнктивно.

Чрез

възможността

да

установява маски

за всяка

отделна

външна ЗП,

програмистът

може да

управлява

достъпа на

едни или

други външни

устройства

до текущо

изпълняваната

програма.

Построяването на контролера на прекъсванията може да се осъществи на практика въз основа на два подхода. Според първият подход, функциите на контролера са съсредоточени в едно конструктивно завършено устройство, а според втория подход - функциите са разпределени между процесора и контролерите на външните устройства.

Система

за

прекъсване с

централизирани

функции

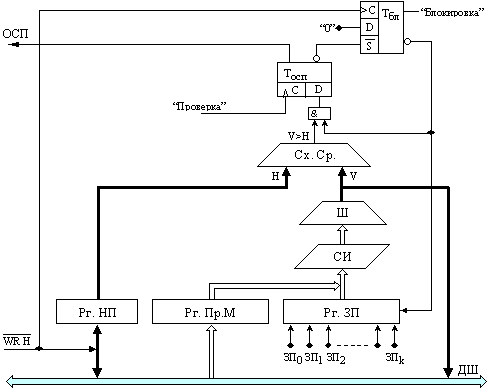

На фигура 5.4.4.1 е показана обобщена логическа структура на програмируем контролер на прекъсванията с централизирани функции.

Фиг. 5.4.4.1. Обобщена

логическа

структура на

програмируем

контролер на

прекъсванията

Както

се вижда от

рисунката, в

неговата операционна

част влизат:

регистър за

фиксиране на

заявките Рг.ЗП;

регистър на

програмните

маски Рг.Пр.М;

регистър за

ниво на

приоритета Рг.НП;

схема за

избор на

най-приоритетната

заявка СхИ;

шифратор Ш;

схема за

сравнение

(компаратор) Сх.Ср. и

два тригера с

динамично

управление

по преден

фронт,

реализиращи

сигналите ОСП и "Блокировка".

Регистърът

на заявките и

регистърът

на програмните

маски са (k+1)-разрядни.

Най-приоритетен

е входът с

номер 0.

Разрядността

q

на регистъра

на нивото се

определя от

броя на

заявките,

според

формулата

![]()

Представената

логическа

структура

работи по следния

начин. Нека

без загуба на

общност първоначално

да

предположим,

че в

регистъра за

ниво на

приоритет е

записана

нула (Рг.НП)=0,

тригерите ТОСП

и ТБЛ

са нулирани и

в регистъра Рг.ЗП

няма

фиксирани

заявки за

прекъсване

(Рг.ЗП)=0, а в

регистъра на

програмните

маски има

само единици.

В

това

състояние

комбинационната

логика на

контролера е

получила на

изхода на

компаратора

отговорът на

въпроса V<H?. Там има

единица ако V<H, и нула

във всички

останали

случаи.

Единицата на

този изход

означава, че

има заявки за

прекъсване,

че те не са

маскирани и

че избраната

най-приоритетна

от тях

наскача

текущото

ниво за

приоритет. По

тази причина

трябва да

бъде

обезпокоен

процесорът.

По инициатива

на процесора

(или друго

интерфейсно

устройство),

в даден

момент се

получава

сигналът "Проверка".

Предният

фронт на този

сигнал

записва в тригера

ТОСП

резултата от

работата на

комбинационната

логика. В

случая на

изходното

положение при

изказаните

по-горе

условия, т.е. при

липса на

фиксирани ЗП,

в тригера се

записва нула

–

проверяваното

отношение (V<H) не е

вярно.

Схемата

ще се намира

в това

състояние

въпреки

многократните

проверки,

докато не се

получат

заявки за

прекъсване.

Колкото по-приоритетна

е избраната

заявката,

толкова по-голямо

тегло има

формираният

от шифратора

код. Ако този

код

надхвърля по

стойност

кодовата

комбинация

на

установеното

в Рг.НП

от

програмата

ниво за

прекъсване,

на изхода на

компаратора,

както вече

казахме, ще

се получи

единица. С

постъпването

на сигнал "Проверка",

в тригер ТОСП ще

се запише

единица.

Правият

изход на този

тригер, в

качеството

си на сигнал

ОСП, се изпраща

в процесора,

на входа INT.

С

излизането

на сигнала ОСП,

блокиращият

тригер ТБЛ се

установява

също в

единично

състояние. Нулата

от инверсния

изход на този

тригер

блокира

приемането

на нови заявки

за

прекъсване в Рг.ЗП,

а така също

забранява

информационния

D вход

на тригера ТОСП.

Следващият

сигнал "Проверка"

ще запише

нула в този

тригер, а

тригерът ТБЛ

ще

продължава

да удържа

своето

състояние. Състоянието

на

контролера

не се променя

-

в процесора

протича

процес на

осъществяване

на

прекъсването, т.е.

изпълнява се

МППОП, при

което в стека

се запомня

старото

състояние и

се установява

новото. За

целта, от

контролера

на прекъсванията

се прочита

номерът V на избраната

заявка. Чрез

него в

процесора се

формира

адресът за

достъп в

таблицата на

векторите за

прекъсване,

то където се

извлича

адресът за

преход АПР

към

съответната

обслужваща

програма. Този

адрес се

записва в

програмния

брояч, с което

по силата на

командния

цикъл се

стартира

обслужващата

програма.

Извиканата

обслужваща

програма е

длъжна да

инициализира

според

своите

изисквания

контролера

на

прекъсванията,

като запише в

него своята

програмна

маска и

своето ниво

на приоритет

за

прекъсване.

Преди това обаче

тя трябва да

съхрани

нивото на

приоритет за

прекъсване

на

прекъсваната

програма,

намиращ се в Рг.НП,

за да може в

последствие

работата й да

бъде

възобновена

правилно.

Сигналът not(WR_H),

който

записва в

стека кода на

нивото, е причина

да се нулира

тригерът за

блокировка, с

което се

разрешава

достъпът на

нови заявки

за

прекъсване в

регистър Рг.ЗП,

както и

записът на

съобщението

за избор в тригера

за

прекъсване ТОСП.

Обслужващата

програма,

която е

стартирана в

процесора, е

длъжна да

запише код на

ниво за прекъсване

по-висок от

този на

прекъснатата

програма. Ако

това съотношение

не е

изпълнено, е

възможно да се

приеме

същата

заявка (ако

не е

постъпила по-приоритетна)

от същия

източник,

който междувременно

вече се

обслужва.

Тази ситуация

вече

описахме. Тя

може да

доведе до насищане

(зацикляне)

на системата

за

прекъсване.

Ето защо

стартиралата

програма за

обслужване

трябва да

прекрати

сигнала ЗП,

постъпващ от

обслужваното

устройство,

или да го

маскира в Рг.Пр.М, така

че

зациклянето

да бъде

предотвратено.

Практикува

се още една

възможност –

промяна на

приоритета

му в по-нисък,

при което в

описаната

структура

тази заявка

вече не би

могла да се

приема.

Ако

по време на

така

приетата

заявка за прекъсване

постъпи нова

заявка, която

има по-висок

приоритет от

установеното

в Рг.НП

ниво, то

процесорът

ще изпълни по

същата процедура

прекъсване

на

обслужващата

програма и ще

предаде

управлението

на новата обслужваща

програма. С

други думи

новото прекъсване,

като

по-приоритетно,

ще бъде вложено

в

предидущото.

След

като

обслужващата

програма

завърши по

същество

своята обработка,

преди да

изпълни

последната

команда - "Връщане

от

прекъсване", тя

трябва по

програмен

път да снеме

програмните

маски, които

е поставила в

Рг.Пр.М

и да

възстанови в Рг.НП

нивото на

приоритет на

програмата, към

която се

осъществява

връщане. С

други думи,

процесът на

връщане от

прекъсване е

обратен на

преди това

изпълнения

преход.

В

логическата

структура на

разгледания

контролер не

са показани

адресните

дешифратори

към

програмно

достъпните

регистри и

данновият

буфер. От

гледна точка

на процесора

(т.е. на обслужващите

програми),

контролерът

на прекъсванията

представлява

три клетки в

паметта, в

които той

може да

записва, или

от които може

да чете -

клетка за

програмните

маски, клетка

за ниво на

приоритета и

клетка за

номер на

вектор.

Наличието на

контролер на

прекъсванията

от описания

вид позволява

процесорът

да има само

един вход за

прекъсване и

едно ниво.

В

реалните

системи

контролерът

на прекъсванията

се запечатва

в отделна

интегрална

схема, към

която са реализирани

обикновено 8

входа за

постъпване на

ЗП (IRQ). В

тази схема

обаче се

добавя още

един регистър - за

режима. Така

контролерът

може да бъде

инициализиран

главен (master)

и подчинен (slave), с което

става

възможно

каскадното

свързване на

няколко

контролера и

увеличение

на броя на

входовете за

ЗП. При

каскада с две

нива може да

се постигне следната

64-входова

схема:

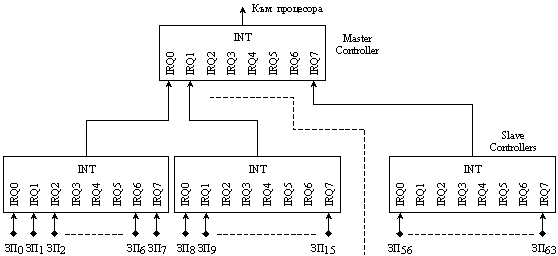

Фиг. 5.4.4.2. Каскадно

свързване на

ПКП

Типичните

режими, в

които може да

се окаже първоначално

инициализиран

контролерът,

са два:

1.

Твърд

приоритет.

В

литературата

може да се

срещне под

обозначението

FNM (Fully Nested Mode), или

още режим на вложени

прекъсвания.

В този режим

най-приоритетно

е прекъсването,

постъпило по

вход с

най-малък

номер. Всяко

следващо с

по-малък

номер може да

прекъсне

обработващото

се в момента,

при условие,

че не е

маскирано.

2.

Циклически

приоритет. В

литературата

може да се

срещне под

обозначението

ARM (Automatic Rotation Mode),

или още режим

на

циклическа

обработка.

Подреждането

на приоритетите

в този режим

е линейно, но

вече не е

фиксирано, а

с възможност

за промяна

след поредната

обработка.

Принципът за

промяна е следният:

приоритетът

на последно

обработеното

прекъсване

(т.е.

приоритетът

на съответният

му вход)

получава

най-ниската

стойност. С

други думи,

след

обработката,

заедно с всички

преди него,

се нарежда

най-отзад.

Така непосредствено

следващият

след него става

най-приоритетен,

ето защо при

едновременно

постъпване

на няколко

ЗП,

предимство ще

имат

заявките,

които преди

това са имали

по-нисък

приоритет.

Приема се, че

в този режим

се постига

“равноправие”

при

обработка на прекъсванията.

Циклическият

режим ще поясним

чрез следния

пример: нека

първоначално

приоритетът

на входовете

е бил подреден

в низходящ

ред отляво

надясно така:

0 1 2 3

4 5 6 7

Постъпва заявка по вход №3.

След нейното обслужване опашката от приоритети продължава да е в низходящ ред отляво надясно, но съответствието им към входовете ще бъде следното:

4 5 6 7 0 1 2 3

Чрез

споменатия

регистър на

режима, в

реалните

контролери

програмистът

може да

управлява

още различни

характеристики,

като

например по кой

фронт на

сигнала ЗП да

се възприема

заявката, или

още дали да

се възприема

по фронт или

по ниво. Самите

системи за

прекъсване

са в непрекъснато

развитие,

така че

читателят

може да се

срещне с

множество

допълнителни

режими.

Система

за

прекъсване с

разпределени

функции

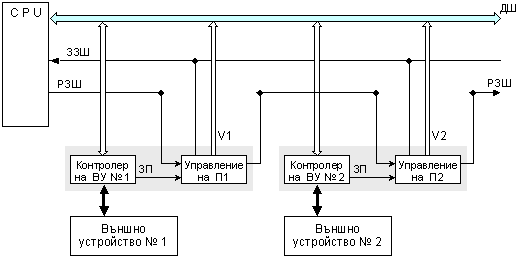

Вторият

подход за

изграждане

на системата

за

прекъсване,

който се

характеризира

с разпределени функции,

води към

логическата

структура

показана на

фигура 5.4.4.3.

Фиг.

5.4.4.3

Обобщена

логическа

структура на

система за

прекъсване с

разпределени

функции

На

фигурата се

вижда, че

външните

устройства

са включени

към

процесора

чрез неговата

системна

шина, с

помощта на

своите

контролери. В

състава на

всеки

контролер на

външно устройство

е включена

схема за

управление на

прекъсването

- СУП. На

рисунката тя

умишлено е

показна

отделно, тъй

като ще бъде

пояснена

допълнително.

Индивидуалните

заявки за

прекъсване(ЗП1, ЗП2, ...),

възникващи по

някакви

причини

(най-често

при

готовност на

устройството

за обмен),

въздействат

на схемата за

управление

на

прекъсването СУП. Всяка

от схемите за

управление

на прекъсването,

получила от

контролера

на външното устройство

заявка за

прекъсване

ЗП, генерира заявка за

заемане на

шината – ЗЗШ. Както

се вижда от

фигурата

по-горе, всички

изходи на

сигналите

ЗЗШ са

свързани "на

късо", т.е. в

общ

проводник чрез

функцията ИЛИ

(опроводено

ИЛИ). Тъй като

по

състоянието

на линията ЗЗШ

процесорът

не може да

разбере кой е

източникът и

колко са

заявките, за

разрешаване

на този

проблем той

използува

еднопосочната

линия разрешение

за заемане на

шината – РЗШ.

На тази линия

процесорът

изпраща

активен сигнал

по време на

изпълнението

на МППОП (вижте

фигура 5.4.1.2).

В

отговор на

сигнал

разрешение

за заемане на

шината РЗШ,

избраното

устройство

трябва да

изпрати по

данновата

шина съхраняващият

се в неговия

контролер,

идентификационен

номер V.

Приемайки

този номер,

процесорът

формира адрес

за преход и

го зарежда в

програмния брояч

с което

осъществява

прехода към

съответната

обслужваща

програма.

От

схемата на

свързване се

вижда, че

устройствата

са свързани

по линията на

сигнала разрешение

РЗШ последователно,

което

означава, че

приоритетът

на така общо

свързаните

към сигнала

ЗЗШ устройства,

е подреден в

низходящ ред,

в посоката на

разпространяващият

се от

процесора сигнал

РЗШ, т.е.

най-приоритетното

устройство е

най-близо до

процесора.

Алгоритъмът

за

прекъсване,

който

реализира

МППОП, в една

система за

прекъсване с

разпределени

функции, се

осигурява от

схемата за

управление на

прекъсването

СУП.

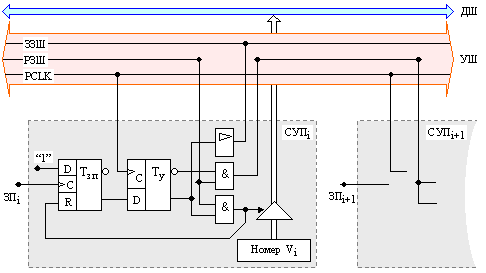

Принципната

логическа

схема на тази

част от

контролера

на външното

устройство е

показана

по-долу на

фигура 5.4.4.4.

Фиг. 5.4.4.4. Принципна

логическа

схема за генериране

на сигнал ЗЗШ

Асинхронната

заявка ЗП, която се

появява в

устройство №i, се

фиксира в

тригер ТЗП.

Следващият

след него

управляващ

тригер ТУ, се

установява

по така

фиксираната

заявка синхронно

по предния

фронт на

интерфейсния (периферния) тактов

сигнал PCLK. Ако

тригер ТЗП е в

единично

състояние,

тригерът ТУ

също се

установява в

единично

състояние, с което

формира

заявка за

заемане на

шината ЗЗШ, като в

същото време

прекъсва

последователното

разпространение

на сигнала РЗШ

към

следващите

контролери (средната

схема И).

Буферната

схема, която

извежда

върху управляващата

магистрала

сигнала ЗЗШ,

технически е

схема с

отворен

колектор (с

отворен сток

или още сорс

за МОП

структури) и

заедно с

другите

аналогични

изходи на

заявки образува

върху

линията ЗЗШ

така

нареченото

опроводено ИЛИ.

С други думи

заявката ЗЗШ,

която

получава процесорът,

е резултат от

дизюнкцията

на всички

заявки,

прикачени

към тази

линия.

При

получаване

на сигнала

ЗЗШ

процесорът прекъсва

текущо

изпълняваната

програма и в

отговор

изпраща потвърждението

РЗШ. Този

сигнал

отваря едновременно

двете схеми И.

Ако в текущия

контролер не

е фиксирана

ЗП, то

съответният

управляващ

тригер е в

състояние

нула. Така

единицата от

неговия инверсен

изход се

разпространява

към следващия

контролер, в

качеството

си на сигнал

РЗШ. Това

разпространение

се повтаря в

следващите

схеми до

срещане на устройство,

което е

подало ЗП.

Ако в текущото устройство има фиксирана ЗП, то управляващият тригер е в състояние единица и неговият инверсен изход предотвратява разпространението на сигнала РЗШ към следващия контролер.

По

същото време

на изхода на

долната

схема И,

изчисляваща

конюнкцията (РЗШ)Ç(ТУ),

се формира

единица. Тази

единица

отваря данновия

буфер на

вектора Vi и по

обратната

връзка

възстановява

изходното

състояние на

тригер ТЗП, като

го нулира.

При

следващия

импулс на

сигнала PCLK, се

нулира и

управляващият

тригер ТУ. Така

векторът Vi е валиден

на данновата

шина в

течение само на

един такт.

В

системи за

прекъсване,

комбиниращи

двата

изложени

подхода, в

процесора са предвидени

няколко

двойки

сигнали (ЗЗШ, РЗШ).

Конфликтите

между тези

двойки, при

повече от

една линия за

ЗЗШ,

се решават

чрез

алгоритъма

на

централизирания

контролер от

фигура 5.4.4.1.

Следващият

раздел е:

5.4.5.

Проблеми на

точното

прекъсване