Последната

актуализация

на този

раздел е от 2019

година.

4.2.2.

Полупроводникови

динамични

памети.

Първа част

DRAM, SDRAM,

SDR, DDR,

DDR2, DDR3, DDR4,

DDR5

Запомнящ

елемент.

Запомняща

клетка. Примерни

схеми.

Основни

операции

Вече

представихме

запомнящия

елемент в

статичните

памети - електронна

схема, която

в логически

смисъл представлява

тригер.

Основния

недостатък

на този вид

запомнящи

елементи е

големият

брой

електронни

елементи,

които го

реализират. С

други думи

при

реализацията

си електронната

схема на

запомнящия

елемент

заема значителна

площ върху

силициевата

подложка. Това

в крайна

сметка води

до

невъзможността

да бъдат

реализирани

ЗУ с голям

обем. Желанието

за

отстраняване

на този

недостатък и

уплътняване

на

кристалната

площ кара изследователите

да търсят

друга

реализация

на запомнящия

елемент. Така

от

електронните

схеми се

отива към

електронните

елементи.

Най-простичкият

електронен

елемент,

който има

свойството

паметливост,

това е

кондензаторът.

Ние тук се

надяваме, че

читателят

има съответното

познание за

този

електронен

елемент,

затова ще го

представим

кратко.

Кондензаторът

се образува

от две плоски

повърхности

разделени с

тънък слой

диелектрик

(изолатор).

Конструкцията

се изпълнява

в различна

форма, което

зависи от

стойността

на капацитета,

който е нужно

да се

постигне.

Формата на

практика е

правоъгълник

(правоъгълните

ленти

обикновено

са навити

като руло),

кръг или др.

Всяка една от

повърхностите

е свързана с

проводник

(анод, катод).

Едно от

прилаганите

условни

графични

означения на

този

електронен

елемент е

показано

по-долу.

![]()

При

подаване на

напрежение

към изводите

на

кондензатора,

в следствие

на

протичащия ток,

в него

започва

натрупване

на електрически

носители.

Така в една

от

пластините

настъпва

обедняване, а

съответно в

другата,

натрупване

на тези носители.

Процесът се

нарича зареждане

на

кондензатора.

Ако

електрическата

веригата за

зареждане на

кондензатора

бъде

разкъсана,

както е показано

на дясната

рисунка

по-горе,

натрупаните

в

кондензатора

електрони не

могат да възстановят

динамичното

си

равновесие и

остават

“затворени” в

кондензатора.

Разбира се,

на практика

обаче

колкото и да

е добър изолаторът

между двете

пластинки на

кондензатора,

с времето

започва

изтичане на

електрони,

процес който

се нарича разреждане.

Борбата на

технологиите

е този процес

да бъде

максимално

забавен, за

да се имитира

възможно

най-добре

паметливостта

на този вид

запомнящ

елемент.

Както

вече

споменахме в

предидущите

раздели,

динамичната

памет DRAM (Dynamic RAM) е

получила

своето

наименование

от принципа

на действие

на нейните

запомнящи

елементи, в

които

паметливостта

се дължи на

електронния

кондензатор.

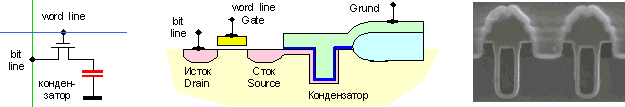

Конструкцията

на полупроводниковия

елемент е

илюстрирана

на долната

рисунка.

Както може да

се види от рисунката,

напречният

срез на

кристала показва

изграждане

на

конструкцията

в дълбочина

на

кристалната

подложка.

Изграждането

на

конструкцията

в дълбочина

съдейства за

не

увеличаване

на схемната

площ. В същото

време

капацитетът

на

кондензатора

може да бъде достатъчно

голям.

Фиг. 4.2.2.1. Схема

и

конструкция

на

запомнящия

елемент

Наличието

на заряд в

кондензатора,

което може да

се установи

върху

данновата

линия (bit line), се

интерпретира

като “1”, а

отсъствието,

като “0”. Простотата

на

електронната

схема

позволява да

се постигне

висока

плътност на

запомнящите

елементи

върху

кристалната

подложка, което

в крайна

сметка

позволява да

се снижи

цената на

относителната

единица обем

от паметта.

Както

вече

отбелязахме

по-горе,

когато клетката

съхранява и

поддържа във

времето своето

съдържание,

т.е. когато

няма обръщение

към нея, по

причина на не

идеалната

изолация, с

течение на

времето

протича

процес, при

който

кондензаторът

се разрежда и

в този смисъл

информацията

се губи. Дори

при отличен

диелектрик в

конструкцията

на кондензатора,

който има

съпротивление

от няколко

тера-ома [TΩ]=(1012[Ω]),

зарядът му се

разсейва

достатъчно

бързо – в

зависимост

от

температурата

от 100 до 10[ms]. Токът

на разряд на

кондензатора

има стойност

не по-голяма

от 10(-10)[A], т.е. 0,1[nA].

Върху

силициевата

подложка

размерите на

кондензатора

са

микроскопични

и капацитетът

му е от

порядъка на 10(-15)[F],

т.е. в

границите на

0,1[pF],

следователно

временната

константа на

електрическата

RC-верига за

разряд на

кондензатора,

е не по-малка

от 1[ms].

Изчислението

на времевата

константа t е

следното

t = (U/I).C = R.C ;

R = U/I ;

R.C = (1012).10(-15) = 10(-3) =

1[ms] .

Този

капацитет

позволява

заряд от

около 40.103 на

брой

електрони. По

причина на

разряда,

периодически

чрез

последователно

обръщение

към всяка

клетка,

стойностите

на потенциалите

във всеки

кондензатор

трябва да се

възстановяват,

т.е. да се

подзареждат, процедура,

която се

нарича опресняване.

Опресняването

на данните

следва да се

извършва на

всеки от 2 до 10[ms],

т.е. от 100 до 500

пъти в

секунда. Така

паметта може

да помни и да

изпълнява

основните

операции

запис и

четене само в

режим на

динамична

(периодична)

регенерация

или опресняване.

Този

непрекъснато

протичащ процес

поддържа

паметта в работно

състояние.

Върху

процеса

опресняване

ще се върнем

по-нататък

отново.

И

тук искаме да

предупредим

читателя, че

на приведените

по-горе

числови

оценки за стойностите

на отделните

величини той

следва да

гледа като на

ориентировъчни.

Вследствие

на развитието

на

интегралните

технологии,

което ще

проличи от

изложението

по-долу,

актуалните

за момента

оценки

следва да се

разглеждат

при

условията на

съответния

производител,

което излиза

извън нашите

цели тук.

Изясняването

в дълбочина

на строежа и

функционирането

на DRAM-паметите

тук не е

нашата

задача. Развитието

и

разнообразието

на архитектурата

на паметта,

на корпусите

на самите интегрални

схеми, на

технологиите

за монтажа им

върху

модулите,

както и

цялостната

архитектура

на

интерфейса

на паметта, е

много

динамично и

следва да

бъде обект на

отделно и

специално

разглеждане.

За

подробности

относно

параметрите

на схемите,

както и за

актуалните

стандарти,

читателят

може да следи

на следния

сайт:

(JEDEC) - Joint Electron

Device Engineering Councils

Global Standarts for the Microelectronics

Industry

Достъп до огромна част от документите, съдържащи стандарти, обикновено се получава срещу заплащане. Това обаче не на всеки е във възможностите, ето защо доставянето на актуална информация е изключително трудно занимание.

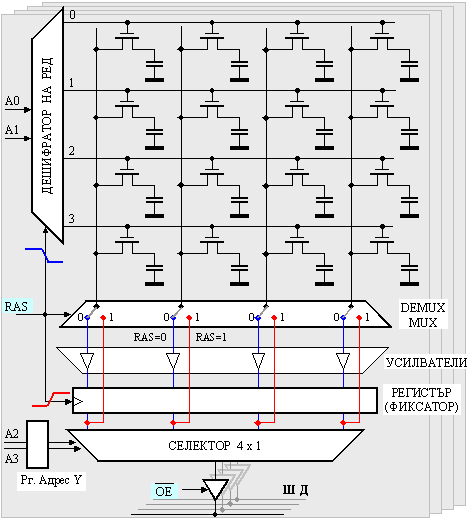

Ще разгледаме опростена общата структура на динамичната памет. На фигура 4.2.2.2 е показан пример на обща принципна схема на DRAM с матрична организация 4х4. Типичният размер (обем) на запомнящия масив на динамичната памет, на практика е с непрекъсната тенденция за увеличаване, по причини, които вече изтъкнахме. Ще поясним кратко функционирането на този тип памет.

Фиг. 4.2.2.2. Обобщена

принципна

схема на DRAM (4х4)х4

(Операция

четене)

При

операция четене

на

съответната

линия за

избор на ред

(А0,А1) от дешифратора

на редовете

излиза

сигнал с високо

ниво. На

рисунката е

показано, че

активирането

(разпространението)

на хоризонталното

разрешение

се извършва

под

управлението

на

стробиращия

сигнал RAS (Row Address Strobe),

в момента на

поява на

неговото

ниско ниво, т.е.

по заден

фронт.

Появата на

високото ниво

върху

гейтовете на

транзисторите

от съответната

клетка

причинява

тяхното

включване.

Включеният

при това към

всяка

вертикална

връзка чувствителен

усилвател за

регенерация (Sense

Amplifaer) възприема

нивото на

снетото от

съответния

кондензатор

напрежение и

го

интерпретира

(формира)

като 0 или

като 1.

Прочетените

при това

стойности от

разрядите на

реда се

записват по

предния

(нарастващ)

фронт на

сигнала RAS в

регистъра-фиксатор,

откъдето по

обратните

връзки се

изпращат

като захранващи

нива върху

транзисторите

на разрешения

ред, при

което

възстановяват

нивата на

напрежение в

съответните

кондензатори.

Последното е

възможно, тъй

като при

високо ниво

на сигнала RAS,

демултиплексорът

DEMUX се е превключил

и осъществил

необходимата

комутация.

Процесът се

нарича “обратен

запис”. В

същото време

адресът на

дешифрираната

колонка (А2,А3)

разрешава

един разряд

от

регистъра-фиксатор,

чието

съдържание

излиза на

данновата

шина през

изходния

буфер при

поява на

разрешаващия

сигнал not(OE).

Следва да се

разбира, че

при

матричната

организация

на

запомнящия

масив, 4-те

бита на разрешената

клетка са

разположени

в дълбочина,

при което

прочетеното

съдържание

от съответната

клетка, е 4

битово.

При

операция запис

в

регистъра-фиксатор

се внася

съответният

даннов бит dj

от входния

регистър за

данни. При

това активна

роля играе

сигналът CAS (Column Address

Strobe).

Останалата

част от

операцията е

аналогична

на вече описаното

по-горе. Този

вариант на

превключванията

е показан на

фигура 4.2.2.3. От

казаното до

тук може да

се заключи,

че основното

закъснение в

тази памет се

дължи на

операция

четене.

Закъснението

се дължи

главно на бавното

освобождаване

на

натрупаното

в кондензатора

електричество

(разреждане).

Фиг. 4.2.2.3. Обобщена

принципна

схема на DRAM (4х4)х4

(Операция

запис)

Както вече стана дума, на структурно ниво динамичната памет е организирана матрично. Входният адрес на клетката вътрешно се интерпретира като съставен от две части – адрес на редовете и адрес на стълбовете. В тази връзка, вътрешното управление на паметта манипулира адреса и входните управляващи сигнали, като изработва съответните вътрешни управляващи сигнали. Управлението на основните операции с оперативната памет се извършва от контролер на паметта. Неговите структурни елементи в различните компютърни системи могат да са разположени в централния процесор, в схемите на самата памет или в отделно произведени интегрални схеми, в частност в чипсетите. Основните операции най-общо казано протичат в следната поетапна последователност:

1. Приемане

на адреса и

кода на

операцията.

Разпространение

към ядрото на

адреса на реда;

2. Формиране

на сигнал RAS;

3. Разпространение

към ядрото на

адреса на стълба;

4. Формиране

на сигнал CAS;

5. Деактивиране

на сигналите

RAS и CAS.

Указаната последователност обаче не изчерпва напълно действията, свързани с опресняването на вътрешното съдържание на клетките на динамичната памет, за което ще кажем по-надолу.

Ускоряването на изпълнението на основната операция (преди всичко операция четене) се търси чрез следните основни подходи:

1. Последователен режим;

2. Регистров режим;

3. Бърз постраничен режим;

4. Пакетен режим;

5. Конвейерен режим;

6. Удвояване на скоростите.

Последователен режим за четене (Flow through Mode)

Действията в този режим вече бяха описвани. Това е базата за сравнение. Последователния режим е вариант на класическия достъп в синхронни памети. Адресът и външните управляващи сигнали се подават до появата на тактовия импулс. По предния фронт на появилият се тактов импулс входната информация се записва във вътрешните регистри (за адрес, за данни). Този преден фронт маркира началото на цикъла на операцията. След съответното време, определено от латентността на схемите, данните се появяват на изходната шина.

Регистров режим за четене (Register to Latch)

Този режим се прилага рядко. Паметите, използващи този режим, се отличават от предходните, по това, че имат изходен регистър. Прочетените данни се съхраняват в този регистър по време на тактовия импулс и се извеждат на изходната шина при задния му фронт. Това дава възможност чрез регулиране на продължителността на тактовия импулс да се регулира закъснението, с което данните излизат на шината.

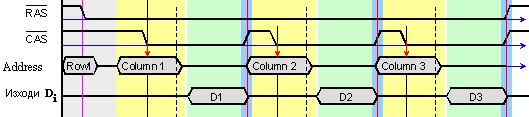

Бърз постраничен режим за четене (Fast Page Mode)

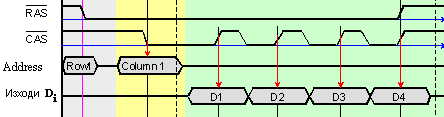

Тук под страница се разбира съвкупността от всички запомнящи елементи в един ред на запомнящата матрица (в ядрото на паметта). Последователните елементи в страницата (в реда) са елементи в клетки с последователни адреси. Така, при достъп към клетки с последователни адреси, процесът може съществено се да се ускори. В този случай съседната клетка може да се адресира само чрез адреса на нейния стълб. Адресът на стълба се съпровожда от сигнал CAS, който може да се появява няколкократно, докато сигнал RAS е постоянен и съответства на адресирания ред. Четенето на блок данни от последователни клетки в този режим е илюстрирано на следващата фигура. Посочените в цвят ивици показват времевите интервали за съответните дейности.

Фиг. 4.2.2.4. Операция

четене в бърз

постраничен

режим (FPM DRAM)

Паметите, означени FPM DRAM, се появяват през 1995 година. Паметта работи на честоти 25 и 33[MHz], позволяващи време за достъп 70 и 60[ns].

Вариант на този тип памети е паметта с усъвършенстван изход EDO DRAM (Extended Data Out DRAM). Нейното приложение започва от 1996 година. Работната честота на тази памет е 40 и 50[MHz] с време за достъп 60 и съответно 50[ns]. Характерно за тази памет е, че изходите й са буферирани с Latch-регистър, който позволява конвейеризация при операция четене. Това води до увеличение на производителността до 15%.

Прилагането на този режим в синхронни DRAM, т.е EDO SDRAM е позволило да се удовлетворят стандартите за работни честоти 66, 100 и за 133[MHz] и време за достъп 40 и 30[ns].

Интегрални схеми, които реализират описания режим, както и негови модификации е прието да се характеризират с формулата x-y-y-y. Първото число показва броя на тактовете на системната шина, които са необходими за достъп до първата клетка в последователността. Следващите 3 числа показват броя на тактовете за достъп до всяка следваща клетка. Указаната формула съдържа така наречените тайминги, за които ще бъде казано по-нататък в изложението.

Пакетен режим за четене (Burst Mode)

В този режим, в отговор на зададен конкретен адрес, паметта връща пакет от данни. Първата прочетена комбинация е съдържанието на подадения адрес. Следващите няколко комбинации, които излизат на данновата шина, са съдържания на следващите няколко последователни клетки, чиито адреси се получават от последователно инкрементирания начален адрес. Например 4 последователни адреса (един адрес в 4 банки):

xxxxx…xxx 00

xxxxx…xxx 01

xxxxx…xxx 10

xxxxx…xxx 11

Ще припомним, че тук под определението последователни, се имат предвид клетки в един и същи ред. Дължината на блока (броя на прочетените клетки) може да се задава и обикновено е 1, 2, 4 или 8. В този режим времето за четене се съкращава няколкократно.

![]()

Фиг. 4.2.2.5. Операция

четене в

пакетен

режим

Както се вижда от времедиаграмата на този режим, сигналът CAS се появява няколкократно на фона на непроменящия се сигнал RAS. В синхронните DRAM памети (SDRAM) циклите на опресняване се изпълняват за всички клетки в един ред под управлението на вътрешен брояч на стълбовете. Масовото производство на синхронни динамични памети започва през 1993 година.

Конвейерен режим за четене (Pipeline Mode)

В този режим процесът се разделя на два етапа. Докато данните от предидущия цикъл на операция четене се предават по външната шина, се приема заявката на следващата операция четене. По този начин два цикъла за четене се припокриват във времето. Така в този режим работната честота може да превиши тази при последователния режим.

Режими

с удвояване

на честотите

Практически всички съвременни памети прилагат подхода на удвоената честота DDR (Double Data Rate). Същността се състои в предаване на данни и по предния и по задния фронт на синхронизиращия импулс (или на друг някакъв вътрешен сигнал). Така в рамките на един период се отчитат два трансфера на данни и честотата за достъп се приема за двукратно увеличена. Този подход е приложен най-напред в синхронните памети, които започват да се означават DDR SDRAM. Получава се така, че при входна честота от 100[MHz] например, работната честота на операция четене е 200[MHz].

Същността на този режим за ускоряване на основните операции в паметта ще поясним по-надолу в изложението на темата.

Опресняване

(регенерация)

на

динамичната памет

Въпреки

че при четене

и при запис

запомнящите

елементи се

опресняват,

случайното

обръщение

към паметта

не може да

гарантира регулярността

на

опресняването

на всеки запомнящ

елемент за

всеки 2[ms]. Това е

самостоятелен

проблем и той

се решава

отделно със

специални

апаратни

средства.

Тези

средства

гарантират

регулярността

на цикъла на

опресняване.

В структурата

на паметта е

добавен

брояч на адреса

за

опресняване.

По същество

съдържанието

на този брояч

адресира

само

редовете в

адресната

матрица. Това

става в един

безкраен

цикъл, при

който след

всяко

опресняване,

към него се

прибавя

единица. В

този процес

адресът по

колони не е

необходим,

тъй като

опресняването

се извършва

едновременно

върху всички

запомнящи

елементи в

клетката (в

реда). Нещо

повече

процесът

протича паралелно

във всички

интегрални

схеми на запомнящия

модул (всички

банки),

изграждащи в дълбочина

запомнящото

устройство (вижте

фигура 4.2.5). По

време на

цикъла за

опресняване

изходите на

паметта към

данновата

шина са

изключени.

Това

означава, че

ако е започнал

цикъл на

опресняване

не са

възможни за

изпълнение

основните

операции в

RAM-паметта, т.е.

те могат да

бъдат

забавени, а

това е определен

недостатък.

В различните интегрални схеми, изграждащи динамичната памет, се прилагат три основни метода за нейното опресняване:

·

Опресняване

ROR (RAS Only Refresh)

с помощта на

един сигнал RAS (Row

Address Strobe);

·

Опресняване

CBR (CAS Before RAS)

с помощта на

сигнала CAS (Column Address Strobe),

който

изпреварва

сигнала RAS;

·

Автоматично

опресняване

SR (Self Refresh).

Опресняването

от тип ROR е

най-рано

използвания

метод. То се

изпълнява по

следния

начин – на

адресната

шина се

поставя

адреса на реда,

който ще се

“освежава”. В

същото време

адресът се

съпровожда

от сигнал RAS.

Така данните

от

запомнящите

елементи в

отворения

ред

постъпват

във

вътрешните

вериги на схемата

и по

обратните

връзки се

записват обратно.

Тъй като по

това време

сигналът CAS отсъства,

не се

изпълнява

цикъл на

основна

операция

(четене /

запис). В

следващ такт

на адресната

шина се

поставя

адреса на

следващия

ред. След

изчерпване

на редовете,

цикълът на

опресняване

се повтаря

многократно от

началния

адрес. При

този метод

адресът се

подава по

адресната

шина от

адресен брояч,

който се

съдържа вън

от паметта,

обикновено в

контролера

на паметта.

Тази

организация

има

недостатъка

да блокира

основните операции

четене /

запис, които

други устройства

искат да

изпълняват.

Така

опресняването

забавя

изпълнението

на

програмите.

Този метод за

опресняване

е фиксиран и

за него регулиращи

опции в “BIOS Setup”

няма. Към

настоящия

момент вече

почти не се

прилага.

Особеното

в метода CBR (опресняване

с

изпреварващ

сигнал CAS) се

състои в

това, че ако в

обикновения

цикъл за

обръщение

към паметта

сигнал RAS

винаги

предшества

сигнал CAS, то при

появата на

сигнал CAS

винаги

започва

специален

цикъл на

опресняване.

В този цикъл

адрес на ред

не се подава,

тъй като

логическата

структура

използва

свой

вътрешен

адресен

брояч, чието

съдържание

(адрес) се

модифицира (+1)

при всеки

CBR-цикъл. При

този метод

регенерацията

не заема

адресната

шина на

паметта.

Автоматическото

опресняване

SR е свързано със

захранващата

система.

Когато

системата

преминава в

режим на

ниска

консумация ("заспива"

- suspend),

тогава

тактовият

генератор не

работи. Така

при отсъствие

на сигналите

RAS и CAS методите ROR

или CBR са невъзможни

и тогава

системата се

регенерира

самостоятелно,

стартирайки

собствен тактов

генератор,

чрез който

паметта се

управлява

отвътре.

Обикновено производителите уточняват, че всеки ред трябва да се обновява на всеки 64 ms или по-малко, според стандарта JEDEC (Foundation for Razvoj Semiconductor Standards). Логиката за обновяване обикновено се използва с DRAM за автоматизиране на периодичното опресняване. Това прави веригата по-сложна, но този недостатък обикновено се компенсира от факта, че DRAM е много по-евтина и с по-голям капацитет от SRAM. Някои системи обновяват всеки ред в тесен цикъл, който се появява веднъж на всеки 64[ms]. Други системи обновяват по един ред по време - например, система с 213=8192 реда ще изисква честота на опресняване на един ред на всеки 7,8[µs] (64[ms]/8192 реда). Няколко системи в реално време опресняват част от паметта в даден момент на базата на външен таймер, който управлява работата на останалата част от системата, като например интервала за вертикално запълване, който се случва на всеки 10 до 20 ms във видео оборудването. Всички методи изискват някакъв вид брояч, за да следите кой ред е следващият, който трябва да се обнови. Повечето DRAM чипове включват този брояч; по-старите видове изискват външна логика за опресняване, за да задържат този брояч. При някои условия по-голямата част от данните в DRAM могат да бъдат възстановени, дори ако DRAM не е обновена за няколко минути.

Задачата за опресняване на данните в клетките на паметта (DRAM) е поверена на устройството за управление на паметта (контролер на паметта). Този контролер е част от схемното оборудване на дънната платка или е интегриран в схемата на процесора. Той е настроен на съответните промишлени стандарти за честотата на опресняване. При разпределено опресняване интервалът между циклите за опресняване може да се определи по следната формула

<интервал

на

опресняване> =

<време за

опресняване>

/ <брой на редовете в паметта>

Например,

поколението

DDR чипове има

време за

опресняване

от 64[ms] и 8192 редa в

паметта, така

че интервалът

на

опресняване

е:

64.10(-3) / 8192 = 7,8125[µs]

В поколението чипове след 2012 година режимът ROR вече е премахнат и за генериране на обновяване се използва вътрешен брояч.

Системите на базата на микропроцесорите на компания Intel традиционно притежават контролер на паметта, който има за задача да се грижи за опресняването. Той е вграден в чипсета (северен мост). Други производители (DEC, AMD, IBM), а така също и Intel-Core-i7, интегрират контролера на паметта в микропроцесорния чип. Това поражда нови проблеми за вече произведени дънни платки, които са свързани с това, че вграденият контролер изисква работа само с даден тип памети.

Една от новите (2018 г.) технологии за опресняване е технологията PASR (Partial Array Self Refresh) на фирмата Samsung. Технологията е предназначена за SDRAM чипове с ниско енергопотребление. Същността й се състои в това, че опресняването се изпълнява само в онези банки на паметта, към които няма обръщения, и в които има заредени данни. Заедно с тази технология се практикува още методът TCSR (Temperature Compensated Self Refresh), който е предназначен за регулиране на скоростта на опресняването в зависимост от работната температура на процесора.

Архитектура на динамичната памет

От

казаното до

тук

читателят

навярно разбира,

че

динамичната

памет е

твърде

сложно устройство,

което се

нуждае от

тематична илюстрация

в

най-различни

направления.

Ето защо ще

ни се наложи

да надникнем

по-дълбоко в

темата, тъй

като всеки

желае да

използва

най-доброто

произведение

на пазара.

За внедряване на нови архитектури на производителите са необходими от около 4 до 5 години. Освен това на всеки 2 години в производството се внедрява и нов технологически процес.

Синхронната

динамична

памет се

появи след 1995

година. В

масово

производство

беше внедрена

паметта SDR SDRAM (Single Data

Rate SDRAM) на

честота 66[MHz],

означавана PC66.

Скоро тази

памет беше

заменена с

по-бързите PC100, а

в

последствие

с PC133. Паметта

има тайминги

5-1-1-1. Захранването

е 3,3[v], a модулите,

в които се

опакова са

168-пинови.

Производственият

обем на схемите

до 2000 година се

намира в

границите на

от 64[MiB] до 256[MiB].

През 2000

година SDR SDRAM

беше заменена

от новата DDR SDRAM (Double

Data Rate SDRAM), имаща

по-голяма

пропускателна

способност и

по-ниско

енергопотребление.

Данновата шина

на паметта е 64[b],

захранването

е 2,5[v] и се опакова

в 184-пинови

модули.

След

архитектурата

DDR се появи

архитектурата

DDR2, за която

бяха

разработени

DDR2-400. Захранването

на тази памет

е 1,8[v] и се

опакова в

240-пинови модули.

Последваха

усъвършенствани

схеми DDR2-533, DDR2-667, DDR2-800 и

даже DDR2-1066.

Практически

всички

производители

на модули с

динамична

памет

използват и

приемат като стандартна

паметта DDR2. В

годините

след 2005 г. тази

памет

започна да се

измества от

паметта DDR3. В

този план на

усъвършенстване

след 2007 година

започна

масовото

внедряване

на паметта с

архитектура

DDR3. Обемът на

паметта при този

стандарт се

движи от 512[Mib] до

8[Gib]. Работните честоти

на DDR3 са

фиксирани – 1333, 1600,

1866 и 2133[MHz].

Следващата

(2012 година)

генерация

памети е DDR4. Тъй

като паметта

е зависима от

типа на микропроцесора

и от типа на

чипсета в

компютърната

система,

масовото

навлизане на

този стандарт

все още не е в

пълна сила.

Той практически

няма

ограничение

на работната

честота -

средно 3000[MHz].

Обемът на

паметта при

този стандарт

се движи от 4

до 8[Gib].

Захранващото

напрежение

на схемите е

1,2[v]. Максималният

обем памет DDR4,

който може да

се инсталира

в едно РС

достига до 512[GiB].

А в

началото на 2019

година

компания Samsung

обяви, че има

готовност да

произвежда

памети от тип

DDR5. Схемите са

означени LPDDR5 DRAM и

засега се

предвижда да

се използват

в

устройствата

за мобилни

комуникации

5G и в

устройства с

изкуствен

интелект. Интегралните

схеми ще имат

обем от 2[Gib] до 32[Gib]

и ще се

произвеждат

по

10-нанометрова

технология. Паметта

ще осигурява

предаване на

данни със

скорост до 6400[Mb/s].

За LPDDR5 DRAM са

предвидени 2

модификации –

със скорост 6400[Mb/s]

и със скорост

5500[Mb/s] при

захранващо

напрежение

от 1,1[v].

Стандартът

JEDEC DDR5 в момента

се

разработва в

Комитета на JEDEC

под номер JC-42.

Той ще

предложи

подобрена

производителност

с по-голяма

енергийна

ефективност

(до 30%) в сравнение

с предишните

поколения DRAM

технологии.

Както е

планирано, DDR5

ще осигури

двойна широчина

на

честотната

лента и

плътност в

сравнение с DDR4,

както и

подобрена

ефективност

на каналите.

Тези

подобрения,

комбинирани

с по-удобен

за

потребителя

интерфейс за

сървърни и

клиентски

платформи, ще

позволят

висока

производителност

и подобрено

управление

на

захранването

в широк

спектър от

приложения.

Краткият

преглед

показва

изключителният

прогрес в

развитието

на запомнящите

устройства.

Адресация

на паметта

Тъй

като в

модулите с

памет се

използват няколко

интегрални

схеми, а в тях

има по няколко

банки, от

първостепенно

значение е

адресирането

на

интегралната

схема и на

банката, в

която се

намира

клетката. За

целта се

използват

сигналите CS, BA0 и

BA1, (BA - Bank Active).

Двубитовата

комбинация

на сигналите

ВА адресира

една от 4-те

банки.

С цел

да бъдат

минимизирани

изводите на

ИС, адресите

на реда и на

стълба се

подава в различно

време по обща

14-битова

мултиплексирана

адресна шина

МА (Multiplexed Address).

Както вече

беше

обяснено,

първо се

предава

адреса на

реда, след

това адреса

на стълба.

Тъй като

логическата

организация

на интегралните

схеми е

различна,

част от

линиите могат

да не се

използват

защото

производителите

ги запазват

за служебни

цели.

Съвременните

памети имат

64-битова

даннова шина,

което е 8[B], а

данновата

шина на

модулите може

да бъде и

по-широка.

Тогава за

постигане на

по-голяма

ширина

отделните

интегрални

схеми са

организирани

по схемата с

общо адресиране.

Получената

памет

обикновено наричат

физическа

банка.

Например, за

образуване

на една

физическа

банка за

64-разряден

модул, са

необходими 16

чипа с ширина

на шината 4[b],

т.е.

организацията

е 64х4. Същата

обща ширина

може да се

получи от 8

чипа с

8-битова

даннова шина

(8х8), или пък 4х16.

Освен

ширината на

данновата

шина, интересен

е

параметърът

обем на

паметта или

на модула.

Така за

64-битова шина

или 8 байта, за

1-гигов обем (1[GiB]),

е необходим

размер от 128[Mi] -

тогава 128х8=1024[MiB], което

е равно на 1[GiB].

Команди

за достъп до

паметта

Сигналите

CS, RAS, CAS, WE и други

подобни се

изработват в

съответната

комбинация

от

съответния контролер

за

управление

на паметта и

следва да се

разбират

като

елементи на

съответната

микрокоманда,

която се

изпълнява в

паметта под

непосредственото

въздействие

на

системната

тактова последователност.

Смисълът на

тези сигнали вече

беше пояснен.

Всяка тяхна

комбинация следва

да се разбира

като КОП (код

на заповяданата

операция). В

следващата

таблица ще поясним

възможните

команди.

Таблица

4.2.2.1.

Микрокоманди

за управление

на паметта

|

not(CS) |

not(RAS) |

not(CAS) |

not(WE) |

BAn |

A10 |

An |

Command |

|

1 |

x |

x |

x |

x |

x |

x |

Задържане

на

микрокомандата

(няма операция) |

|

0 |

1 |

1 |

1 |

x |

x |

x |

(NOP)

Няма

операция. |

|

0 |

1 |

1 |

0 |

x |

x |

x |

Стоп на

текущата

операция за

пакетно

чтене/запис. |

|

0 |

1 |

0 |

1 |

№ bank |

0 |

№ column |

(READ)

Четене на

пакет от

активния в

момента ред. |

|

0 |

1 |

0 |

1 |

№ bank |

1 |

№ column |

(READ)

Четене на

пакет от

активния

ред. Опресни

и затвори

този ред. |

|

0 |

1 |

0 |

0 |

№ bank |

0 |

№ column |

(WRITE) Запис

на пакет в

активния в

момента ред. |

|

0 |

1 |

0 |

0 |

№ bank |

1 |

№ column |

(WRITE) Запис

на пакет в

активния

ред. Опресни

и затвори

този ред. |

|

0 |

0 |

1 |

1 |

№ bank |

№ roud |

(ACTIVE)

Отвори ред

за операция

четене/запис |

|

|

0 |

0 |

1 |

0 |

№ bank |

0 |

x |

(PRECHARGE)

Освободи

текущия ред

в избраната

банка |

|

0 |

0 |

1 |

0 |

x |

1 |

x |

(PRECHARGE)

Освободи

текущия ред

във всички

банки |

|

0 |

0 |

0 |

1 |

x |

x |

x |

Опреняване

по един ред

от всяка

банка, адресирайки

чрез

вътрешния

брояч.

Освободи всички

банки. |

|

0 |

0 |

0 |

0 |

00 |

mode |

Зареди

схемата с

конфигурационните

данни (чрез

линиите от А0

до А9). CAS Latency (2 или 3

такта ) и

дължината

на пакета (1, 2, 4,

или 8 такта) |

|

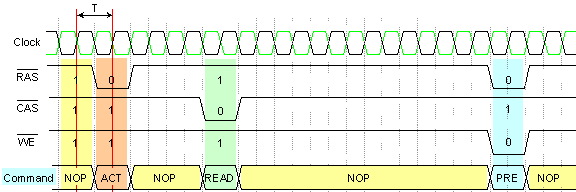

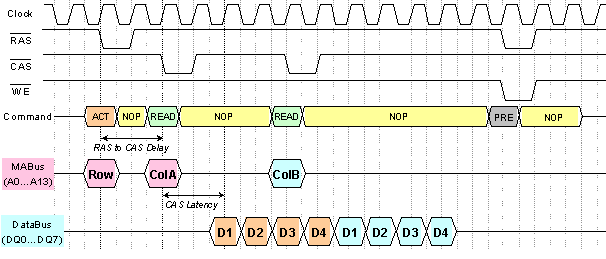

С цел да бъдат опростени времедиаграмите за работата на паметта, често вместо управляващите сигнали се изобразява мнемокода на съответните им микрокоманди. Това съответствие е илюстрирано на следващата фигура.

Фиг. 4.2.2.6. Диаграма

на

съответствието

между сигнали

и

мнемокодове

Основни характеристики на паметта

Главна

характеристика

на паметта е

нейната

пропускателна

способност.

Това е

максималното

количество

данни, което

може да бъде

прочетено от

паметта или

да бъде записано

в нея, за

единица

време.

Пропускателната

способност

на паметта

зависи от ширината

на данновата

шина и от

работната

честота на

паметта.

Количествено

това означава

следното:

например при

модул тип DDR-400,

който има 64

битов

интерфейс

върху 200

мегахерцова

системна

шина, е

възможно да

се осигури

производителност

на трансфера

от порядъка

на 6,4 [GB/s], т.е.

64[b] x 4

x 2.106 = 51200[Mbit/s] = 6400[MB/s]) = 6,4[GB/s] .

Можем

да си

представим

каква ще бъде

стойността

на този

показател

при 128-битова

даннова шина

в комбинация

с 800

мегахерцова

тактова

честота, или

по-висока.

Друга

основна

характеристика

на паметта е

нейната

латентност. В

много случаи

именно

латентността

е

характеристиката,

която преди

всичко определя

производителността

на цялата система,

задминавайки

в това

отношение

тактовата

честота на

дънната

платка.

Под

латентност

следва да се

разбира

закъснението,

което може да

бъде

отчетено

между постъпването

на машинната

команда към

паметта и

подучването

на резултата

от нейното

изпълнение. В

този

интервал, в

който се

развива

алгоритъма на

машинната

команда

обаче има

цяла последователност

от

микрокоманди,

чието изпълнение

не винаги е

безотлагателно.

По едни или

други

причини,

изпълнението

на отделните

микрокоманди

изисква

различно и

непостоянно

време. Освен

това

стартирането

на една микрокоманда

не винаги

започва

веднага. Така

в

последователността

от

микрокоманди

на

алгоритъма

на основната

операция

могат да се

вмъкната

закъснения.

Тъй като

паметта е

синхронна и

основният

двигател на

нейното

функциониране

е тактовата

последователност,

всички

интервали и в

частност

отделните

латентности,

се измерват в

брой тактове

на работната

честота. Така

например, във

времедиаграмата

от

предходната

фигура 4.2.2.6.

ясно може да

се отчете, че

след

микрокоманда

АСТ и

изпълнението

на

микрокоманда

READ изтичат 2,5

периода на тактовата

честота Clock. А

след нея до

изпълнението

на

микрокоманда

PRE изтичат 7,5

такта. Тези

интервали,

означени на

времедиаграмата

с NOP, се наричат тайминги.

Таймингите

са

закъсненията,

които се явяват

между

изпълнението

на отделните

микрокоманди

на

алгоритмите

на основните

за паметта

операции.

Таймминги на паметта

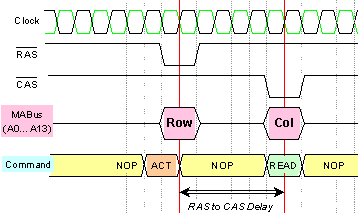

1. Закъснение RAS to CAS Delay (tRCD)

Вече отбелязахме,

че най-напред

следва да се

активира

адресираният

в паметта

ред. За целта

управляващия

контролер

генерира

синхронно с

тактовата

последователност

съответния

набор от

стойности на

управляващите

сигнали

(вижте

таблица 4.2.2.1). В

началото

това е микрокоманда

ACTIVE (not(RAS):=0, not(CAS):=1, not(WE):=1). С

това се

прочита

адреса на

банката и на

реда в нея, и

сигналът от

съответния

дешифратор (в

качеството

си на сигнал

разрешение) активира

запомнящите

елементи. Тук

е необходимо

и полезно да

се разгледат

фигурите в

предходния раздел 4.2.

Следва

подаване на

микрокода READ

или WRITE. Заедно с

това

сигналът not(CAS)

се

превключва в

ниско ниво, с

което се разрешава

подаването

на адреса на

съответния стълб

в

запомнящата

матрица. В

необходимото

ниво се превключва

и сигналът not(WE).

Както може да

се види от

времедиаграмата,

управляващите

сигнали се

превключват

синхронно по

задния фронт

на тактовите

импулси.

Следващият

преден фронт

на съответният

тактов

импулс

фиксира

прочетените

данни в

изходния

регистър – моментът

е означен с

червена

линия. Както

може да се

отчете на

времедиаграмата,

закъснението

на CAS спрямо RAS,

т.е. на READ спрямо

ACTIVE, е 3 такта.

Фиг. 4.2.2.7. Диаграма

на

закъснението

RAS to CAS

Това

закъснение е

опция, която

може да бъде

променяна.

Става дума за

закъснението

на строба not(CAS)

спрямо

строба not(RAS) (RAS to CAS Delay).

Управлението

на дължината

на този времеви

интервал се

използва за

контролиране

на

продължителността

на

същинската

операция –

преходния процес

в запомнящия

масив при

запис, при

опресняване

или при

четене.

Именно

времето, което

се отделя за

този процес

може да бъде

управлявано,

като е

възможно да

му се отделят

2, 3 или 4 такта. Следващият

параметър,

който може да

бъде настройван

е времето на

предварителния

заряд или още

времето за възстановяване

на сигналите not(RAS)

и not(CAS). Тези

сигнали се

възстановяват

(натрупват

заряд) по

време на

високите си

нива.

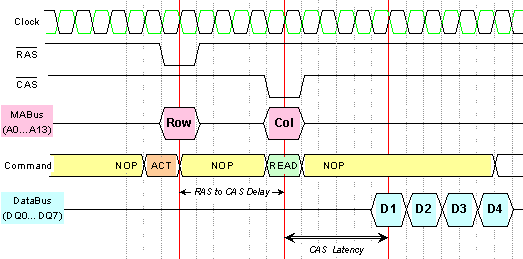

2. Закъснение CAS Latency (tCL)

От

микрокомандата

четене

(запис) на

данни до

издаването

на първата

порция данни

на изходната шина

(запис на

първата

порция данни

в клетка)

изтича

интервал от

време, който

се нарича CAS Latency.

Това

закъснение tCL

е

илюстрирано

на

следващата

фигура. Всяка

следваща

порция данни

се появява на

данновата

шина в

поредния

такт на

сигнала Clock.

Фиг. 4.2.2.8. Диаграма

на

закъснението

CAS Latency

Закъснението

CAS Latency (CL) отразява

за времевата

продължителност

на ниските

нива на

управляващите

сигнали.

Тяхната

продължителност

може да се

настройва

чрез

избиране на

една от следните

стойности: 2, 2,5

или 3 такта.

Същността на

тази

стойност е да

покаже с

какво

закъснение

паметта

трябва да

изпълни

микрокомандата

за четене,

считано от

момента на

нейното

получаване.

Ясно е, че

колкото по-малко

е това време

на очакване,

толкова по-бързо

се изпълнява

транзакцията.

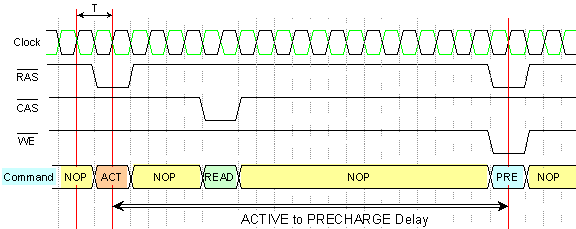

3. Закъснение ACTIVE to PRECHARGE Delay (tRAS)

Това

закъснение е

минималният

времеви интервал,

който трябва

да изтече от

момента на

подаване на

микрокомандата

ACTIVE, която активира

съответния

ред, до

появата на

микрокомандата

PRECHARGE. Това

закъснение

се означава tRAS

и е

илюстрирано

на

следващата

фигура.

Фиг. 4.2.2.9. Диаграма

на

закъснението

ACTIVE to PRECHARGE Delay

Интервалът,

означен TRAS - време

за достъп (Cycle Time)

има

възможност

за настройка

на продължителността.

По същество

това е

времето, през

което е

активиран

даден ред в

запомнящата

матрица, т.е.

това е

времето,

когато редът

е отворен и

достъпен за

пренос на

данни. Този

времеви

интервал

повечето

чип-сети

могат да

определят в границите

от 5 до 15 такта.

Производителността

е по-висока

при малките

стойности на

тази

параметър,

които могат

да бъдат 2, 3 и 4.

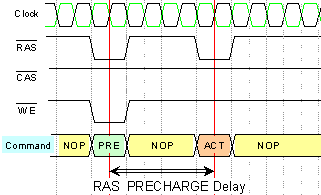

4. Закъснение RAS PRECHARGE Delay (tPD)

Завършването

на цикъла за

обръщение към

банка от

паметта се

изпълнява с

подаване на

микрокоманда

PRECHARGE. Тази

микрокоманда

затваря

обработвания

ред. От

момента на

изчезването

й, и до

постъпване

на нова

микрокоманда

за

активиране

на ред,

изтича

времеви интервал,

който се

нарича RAS Precharge,

който се

означава tPD.

Фиг. 4.2.2.10. Диаграма

на

закъснението

ACTIVE to PRECHARGE Delay

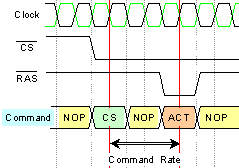

5. Микрокоманда RATE (Command Rate)

Следващият

вид

закъснение,

което трябва

да изясним, е

скоростта, с

която се

изпълнява

микрокомандата

(Command Rate). Това е

закъснението

на активацията

на избрания

ред (ACT) след

появата на

сигнала за

избор на чипа

not(CS). Това

закъснение

се измерва с

един или два такта

на сигнала Clock (1T

или 2T).

Читателят

навярно разбира,

че това

закъснение е

същностно за

електрониката

на паметта,

нещо което не

може да бъде

преодоляно.

Фиг. 4.2.2.11. Закъснение

Command Rate

При

синхронните

памети,

електронното

закъснение,

ако можем

така да се

изразим,

определя

максималната

работна

честота на

паметта.

Двата

периода на

тактовата

последователност,

която може да

се отчете във

времедиаграмата

по-горе,

следва да

осигурят

външно и

принудително

минималната

отсрочка във

времето,

която

физически е

необходима

на

електронните

схеми, за да

изпълнят

съответното

действие с

максимална надеждност.

Следва

списък на

тайминги,

които може да

бъдат

срещнати:

·

tCL: CAS Latency

·

tCR: Command Rate

·

tPTP: Precharge To Precharge Delay

·

tRAS: RAS Active Time

·

tRCD: RAS To CAS Delay

·

tREF: Refresh Period

·

tRFC: Row Refresh Cycle Time

·

tRP: RAS Precharge

·

tRRD: RAS To RAS Delay

·

tRTP: Read To Precharge Delay

·

tRTR: Read To Read Delay

·

tRTW: Read To Write Delay

·

tWR: Write Recovery Time

·

tWTP: Write To Precharge Delay

·

tWTR: Write To Read Delay

·

tWTW: Write To Write Delay

Съотношение

между

таймингите

на паметта

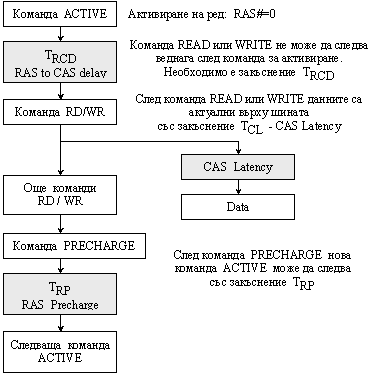

В

терминологията,

която беше

въведена, изпълнението

на операция

четене от

паметта протича

в следната

последователност:

1. Микрокоманда

ACTIVE – активира

адресирания

ред в банка

на паметта;

2. Микрокоманда

READ –

прочита

данните от

отворената

клетка във

вътрешния

регистър;

3. Прочитане

на данните от

външната

даннова шина;

4. Микрокоманда

PRECHARGE –

деактивира адресирания

ред;

5. Микрокоманда

ACTIVE – активира

нов адресиран

ред в банка

на паметта.

Времевият

интервал

между активирането

на реда и

микрокомандата

за четене се

определя от

тайминга tRCD,

а интервала

между

микрокомандата

за четене и

появилите се

на изходната

шина данни се

определя с

тайминга tCL.

Времевият

интервал

между

началото на

четенето и

деактивирането

на реда (tRAS)

зависи от

дължината на

предавания

пакет, при

това се

изисква

изпълнение

на отношението tRAS > tRCD + tCL

.

Минималната

стойност на

тайминга tRAS

следва да

бъде

по-голяма от

сумата tRCD+tCL

с толкова,

колкото е

продължителността

на третата

операция,

която

определя

дължината на

предавания

пакет. Ще

дадем

следния

пример – за

памет от тип SDR (Single

Data Rate) с

тайминги tRCD=2Т и

tCL=2Т

се получава,

че tRAS >

4Т. При

дължина на

пакета BL=2 е

необходимо

време не

по-малко от 2

такта за

предаване на

целия пакет,

така излиза,

че

минималната

стойност на

тайминга tRAS е 6 такта (tRAS = 6Т).

Представяме и блоксхема на алгоритъма на цялостният цикъл на основна операция (четене/запис в/от оперативната памет).

Фиг. 4.2.2.12. Алгоритъм

на основна

операция в DRAM

След

команда за

четене

(запис)

първият елемент

на данните се

явява със

закъснение CAS

Latency. Следващите

елементи на

данните се

явяват последователно

във всеки

такт.

Закъснението

се измерва в

брой тактове.

Обръщението

към банката в

паметта

завършва при команда

Precharge, която

затваря

дадения ред в

паметта. След

нея и до

следващото

активиране следва

да се изчака

времето ROW Precharge –

означавано TRP.

Закъснението TRAS (ACTIVE to Precharge

Delay)

характеризира

времето за

достъп.

Скоростта,

с която се

изпълняват

командите

към паметта (Command Rate), се

оценява със

закъснението

между командата

за избор на

чип not(CS) и командата

за

активиране

на ред. Като

правило, закъснението

Command Rate е един такт

(1Т) или два

такта (2Т) и се

означава

заедно с

таймингите

на

оперативната

памет.

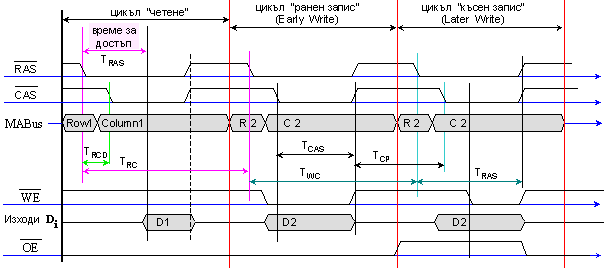

Изказаният DDR-подход става възможен при много високи изисквания към точността на времевите параметри във времедиаграмата на този тип памети. По-долу на фигура 4.2.2.13 са представени “класическите” времедиаграми на операциите запис и четене.

Фиг. 4.2.2.13. Времедиаграми

на операции

четене и

запис в

динамична

памет

Записване

на

таймингите

на паметта

Описаните

по-горе

тайминги

обикновено

се записват

като

последователност:

tCL – tRCD – tRP – tRAS –

Command Rate .

Ето

пример за

модул РС3200 (DDR400)

таймингите

могат да

бъдат 2-3-4-5-(1Т), т.е.

2-3-4-5-1;

CAS

Latency = 2 такта ;

RAS to CAS

Delay = 3 такта ;

RAS

Precharge = 4 такта ;

ACT to

Precharge delay = 5 такта ;

Command

Rate = 1 такт .

Памет от

тип SDR

В

следващите

раздели ще

изложим

малко по-подробно

същността на

наименованията

на различните

типове

динамични

памети, които

вече

многократно

употребявахме.

Ще започнем с

така

обявената SDR

памет (Single Data Rate).

Това е

синхронна

памет чия та

структура е най-проста.

И въпреки че

вече не се

среща, тук ще

бъде

използвана

като база,

върху която ще

изложим

поясненията.

В тази памет

всички

превключвания

на входните и

на изходните

сигнали са

синхронизирани

с

положителния

(преден)

фронт на тактовите

импулси.

Целият масив

на SDRAM-модула е

разделен на

две

независими

банки. Това

структурно

решение

позволява да

се съвмести

извеждане на

данни от

едната банка

с предаване

на адрес в

другата

банка, като

по този начин

има 2

едновременно

отворени

страници

(реда).

Достъпът до

тези 2

страници се

редува (Bank Interleaving) и

по този начин

се

отстраняват

закъсненията,

което

осигурява

непрекъснатост

на потока от

данни.

SDRAM-модули с

тази

организация

се произвеждаха

на две

честоти – РС100 и

РС133.

В

последствие

в този тип SDRAM

памет беше

организиран

пакетен

режим (Burst Mode),

което се

постигаше с

помощта на

вграден брояч

на адреси.

Броят на

адресираните

по този начин

стълбове се

нарича

дължина на

пакета BL (Burst Lenght).

В този

тип памет

ядрото на

схемите и

буферните

регистри за

данни

работят

синхронно на

една и съща

честота (100 или

133[MHz]).

Предаването

на всеки

отделен бит

от буфера

става на

всеки такт.

Като пример

на

следващата

фигура е илюстрирана

работата на SDR

SDRAM при дължина

на пакета BL=4

тайминги tRCD=2 и tCL=2

.

Фиг. 4.2.2.14. Примерна

времедиаграма

за работа на SDR

SDRAM памет

Памет от

тип DDR

Този

тип памет

беше

естественото

развитие на SDRAM.

Обезпечава

двойно по-висока

пропускателна

способност. DDR (Double

Data Rate) паметта,

която има 64

битова

външна шина,

предава по 2

бита на всяка

от линиите

последователно

във времето

синхронно с

предния и задния

фронт на

тактовия

импулс. Така

за един такт

излизат 128

бита. Тъй

като

тригерите в

буферните

регистри не могат

да работят и

по двата

фронта на

тактовия

импулс, а

само по

предния,

излиза, че

тяхното

тактуване

трябва да се

осъществи от

2 пъти

по-висока

честота, за

да се придаде

смисъл на

самото

наименование

на паметта.

Два

предни

фронта в

рамките на

един период на

тактовата

последователност

без вътрешно

да се удвоява

тактовата

честота може

да имаме само

ако

тактовата

последователност

се използва

парафазно.

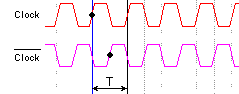

Смисълът на

това

изказване

илюстрира

следващата

фигура.

Фиг. 4.2.2.15. Парафазна

тактова

последователност

(2 предни/задни

фронта в

период)

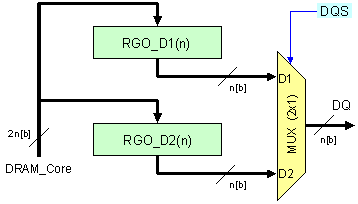

За да

се осъществи

изказаната

идея е необходимо

още от ядрото

на паметта да

бъдат прочетени

два пъти

повече

битове (2n).

Изграждат се

две

независими линии

за предаване

на данни от

ядрото към буферните

регистри.

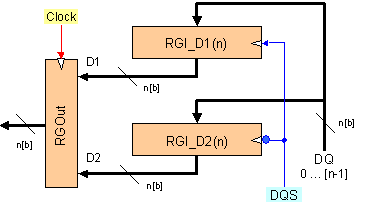

Фиг. 4.2.2.16. Технология

2n-Prefetch при

операция

четене в DDR SDRAM

Фиг. 4.2.2.17. Технология

2n-Prefetch при

операция

запис в DDR SDRAM

Сигнал

DQS (Data Queue Strobe) –

парафазен

стробиращ

данните

сигнал. Той е

управлява

извеждането

на данните

при четене и

въвеждането

им при запис.

Във времето

при четене е

изравнен със

данните, а

при запис е

центрирано

изравнен с

данните. Използва

се за

синхронизация

на данните.

Тези стробиращи

импулси се

генерират от

източника на

данните – при

операция

четене

сигналът DQS се

генерира от

паметта, а

при операция

запис – от

устройството

за

управление

на паметта (от

чипсета). При

четене

фронтовете

на този

сигнал се

центрират

(синхронизират)

точно в

момента на

смяна (поява)

на данните,

при което

приемникът

трябва да

фиксира

(запише) тези

данни с

известно

закъснение

спрямо превключването

на сигнала DQS.

При запис

фронтовете

на този

сигнал се

центрират

точно по

средата на

периода, в

който

съществуват истинните

стойности на

данните. Това

отново

подпомага

приемника, в

случая

самата памет,

кога да

фиксира

получените

данни.

Съществува

още един

особен

проблем със

синхронизацията

на сигнала DQS

спрямо

системната тактова

последователност

Clock (CLK), който се

дължи на

вътрешносхемните

закъснения.

За

отстраняването

му в

структурата

на паметта е

включена

специална

логическа

схема за автонастройка

DLL спрямо

сигнала CLK (DLL - Delay Locked

Loop).

Функционирането

на тази схема

наподобява

така

наречената

фазова

автонастройка

PLL (Phase-Locked Loop), като

осигурява

съвпадение

на

фронтовете на

DQS с тези на CLK.

Възможността

за

автонастройка

DLL в някои интегрални

схеми може да

бъде

изключвана.

Този режим на

работа се

инициализира

в регистъра

на режима на

схемата. Прилага

се когато се

цели

понижаване

на консумацията

тъй като се

работи с

понижена честота.

В този режим

строб

сигналите DQS

не са синхронизирани

с тактовия CLK. В

резултат различните

интегрални

схеми,

работещи върху

една и съща

системна

шина, ще имат

различни

честоти.

Друга

особеност на

DDR паметите е,

че при запис

данните се

подават със

закъснение

поне от един

такт (период),

параметър

наричан Write Latency

(WL).

В тази

архитектура

достъп до

данните се осъществява

по двойки –

всяка

единична

микрокоманда

за четене

води до

отправка по

външната даннова

шина две

порции.

Аналогично

всяка микрокоманда

за запис

очаква

постъпване на

две порции

данни по

външната

шина. По тази

причина

дължината на

пакета BL не

може да надхвърля

числото 2.

В

ядрото

синхронизацията

е само

предния фронт

на тактовата

честота (133[MHz]), но

входно-изходните

буфери се

синхронизират

и по двата фронта

(266[MHz]).

Отличителна

характеристика

на DDR паметта е реализацията

на 4

логически

банки (Bank0-Bank3),

дължината на

пакета е BL=4 и

тайминги tRAS=2

и tRCD=3.

Първоначално

се активира

последователно

всяка една

банка, за да

се получи

достъп до

съответния

ред.

Закъснението

между активацията

на

последователни

банки се

определя от

таймига tRRD (Row to ROW

Delay), който

обикновено

има стойност

2Т. По този начин,

след всеки 2

такта се

активира

нова (следваща)

банка, а след

активацията,

със закъснение

от 3 такта, в

банката се

получава микрокоманда

за четене и

от нея

излизат

данни.

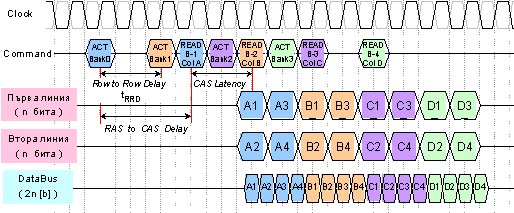

Фиг. 4.2.2.18. Обобщена

времедиаграма

за работа на DDR

SDRAM памет

Тъй

като

закъснението

CAS Latency е 2 такта,

следва че 2

такта след

микрокоманда

READ, данните са

на изходната

шина, както е

показано на

горната

фигура. Ще

обърнем

внимание, че

паметта има

две n-битови

изходни шини,

което означава,

че данните

върху

изходната

шина могат да

бъдат четени

паралелно.

Първата порция

данни (n бита) е

взета от Bank-1,

от стълб Col-A и

се извежда на

първа линия A1

в регистър RGO_D1

(вижте фигура

4.2.2.16). Втората

порция данни

(n бита) е взета

от Bank-2, от

стълб Col-B и се

извежда на

втора линия A2,

едновременно

с първа линия

(следете

времедиаграмата

от фигура 4.2.2.18).

По-нататък,

едновременно

с предаването

по първа

линия на

порцията А3,

по втора

линия може да

бъде

предадена

порцията А4.

Така по първа

линия

следват А1, А3, В1,

В3, С1, С3, D1 и D3, а по

втора линия

следват А2, А4, В2,

В4, С2, С4, D2 и D4.

След

това от

изходните

буфери през

мултиплексора

MUX данните се

извеждат на

външната n-битова

даннова шина

синхронно с

предния и

задния фронт

на тактовата

последователност,

използвайки

парафазния

тактов

сигнал, както

е пояснено на

фигура 4.2.2.15.

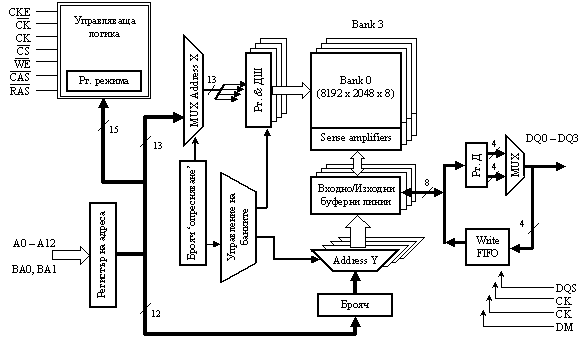

По-долу

на фигура 4.2.2.19 е

представена

вътрешната

логическа

структура на

една от

масово прилаганите

DDR SDRAM памет с

организация

128[Мb]х4. Вижда се,

че запомнящият

масив е

организиран

в 4 паралелни

банки с

8-битови

клетки. Тук е

необходимо

да поясним,

че този масив

е всъщност

тримерен паралелепипед,

в който

8-битовите

клетки са разположени

в дълбочина

на рисунката.

Ето защо

неговите

размери са

означени (8192х2048х8).

Данновият

изход е

4-битов

мултиплексиран.

За

построяване

на модул с

32-битов даннов

изход са

необходими 8

такива

интегрални схеми.

Адресирането

във

вътрешността

на интегралната

схема

изисква

мултиплексиране

на входната

адресна шина,

която е 15-битова.

Адресът на

реда и на

стълба се

приемат чрез

стробиращите

сигнали not(RAS) и not(CAS)

по спадащия

фронт.

Съставът на

сигналите за

управление

на

интегралните

схеми е следният:

CK, not(CK) Парафазен

входен

тактов

сигнал Clock.

Всички

управляващи

и

информационни

сигнали са

синхронизирани

с фронтовете

на този

сигнал.

CKE Clock Enable –

входен

сигнал. Високото

ниво на

сигнала е

разрешение, а

ниското ниво

деактивира

входните и

изходните

драйвери на

схемата. Ниското

ниво

изключва

презареждането

и самоопресняването.

not(CS) Chip Select –

Входен

сигнал за

избор на

схема. Всички

команди към

схемата са

маскирани с

този сигнал.

not(RAS),

not(CAS), not(WE) – Входни

сигнали

(команди).

DM Input Data Mask –

Маска на входните

данни.

ВА0, ВА1 Входове за адрес на вътрешна банка. Определят към коя банка се прилагат командите активиране, четене, запис и презареждане.

А0-А12 Адресни

входове.

DQ0-DQ3 Даннови

двупосочни

линии.

DQS Парафазен

стробиращ

данните

сигнал. Той е

управлява

извеждането

на данните

при четене и

ввъвеждането

им при запис.

Във времето

при четене е

изравнен със

данните, а

при запис е

центрирано

изравнен с

данните. Използва

се за

синхронизация

на данните.

NC Означение

за свободен

пин (No Connection).

Фиг. 4.2.2.19. Логическа

структура на

DDR SDRAM при

организация (128М)х4

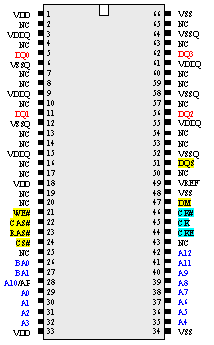

Опаковането

на тази

структура в

корпус тип TSOP66 (Thin

Small Outline Package) е

показано на

фигура 4.2.2.5.

Фиг. 4.2.2.20. Корпус

TSOP66 DDR SDRAM при

организация

(128М)х4

Интегралните

схеми DDR SDRAM се

произвеждат

по технологии

с

дискретизация

под 100

нанометра, и

захранващо

напрежение

от 2,6[v]. Ширината

на шината на

паметта е 64

бита, т.е. за

един такт се

предават 8

байта. Така

получаваме

следната

формула, по

която можем

да определим

скоростта за

предаване: (Тактова

честота на

системната

шина)x2x8.

Към

текущия

момент

корпусите TSOP (Thin

Small Outline Package)

започват да

отстъпват

място на

корпуси тип FBGA (Fine

Pitch Ball Grid Array).

Причината за

тази

конкуренция

се корени в

конструкцията

на TSOP-корпуса.

Същността е в

значително

удължените

във

вътрешността

на корпуса на

интегралната

схема

изходни проводници

(връзки) в

следствие на

вертикалната

странична

подредба на

изходните

пинове. При

корпус от тип

FBGA контактните

пинове

представлява

полусфери с малък

диаметър,

разположени

в

непосредствена

близост до

кристала и

изведени

върху долната

страна на

интегралната

схема. Тези пинове

влизат в

повърхностен

контакт с проводящите

дири върху

платките на

модулите. Така,

поради

скъсеното

разстояние и

повърхностния

монтаж,

работните

честоти на

същите памети

в този тип

корпуси

могат да

бъдат почти

удвоени. По

настоящем

технологията

FBGA е приложена

върху почти

всички

интегрални схеми

и дори върху

единичните

електронни

елементи.

Външният вид

на двата типа

модули е показан

на

фотографията:

Модул

с TSOP-корпуси:

Модул

с FBGA-корпуси:

След

включване на

захранването

по време на

началното

установяване

на

компютърната

система в

работно

състояние се

извършва инициализация

на параметрите

на паметта.

Извършва се

предварително

зареждане

(тест) на

всички банки

на паметта и

се зарежда

(програмира)

регистъра на

режима. Много

от

параметрите

на паметта могат

да се

предопределят

и променят в

така наречената

сет-таблица

на

компютърния

BIOS. По тази

причина

използването

на определен

вид DDR SDRAM се

предопределя

от

възможностите

на

конкретната

интегрална

схема чипсет

да управлява

интерфейса

на модулите

на паметта.

Край

на

изложението

на първа

част. Следва

продължение.

Следващият

раздел е:

ПРОДЪЛЖЕНИЕ:

Полупроводникови

динамични

памети. DRAM, SDRAM, SDR,

DDR, DDR2, DDR3,

DDR4, DDR5